Accanto alle diverse risorse hardware che il componente offre, quali la presenza di timer programmabili, di interfacce LIN-UART, la gestione degli eventi asincroni esterni, la presenza di un convertitore A/D con una risoluzione di 8/10 bit o, ancora, la possibilità di gestire fino a 20 porte di I/O; la presenza del blocco funzionale UART/SIO è, ad ogni modo, una proposta sicuramente utile.

Ogni progettista ha sicuramente la necessità di utilizzare, per le sue applicazioni embedded, sistemi in grado di acquisire informazioni o trasferire le stesse verso sistemi di backup. Questa seriale è abbastanza versatile; infatti, può utilizzare benissimo, mediante la programmazione di un registro dedicato, due differenti modalità di funzionamento: sincrono o asincrono. Le informazioni, poi, sono trasferite utilizzando il formato NRZ, il riquadro 1 mostra alcune considerazioni utili per chi è nuovo a queste cose. Inoltre, per definire il suo rate, è possibile utilizzare o un baud rate generator dedicato o un clock esterno in modalità sincrona.

Introduzione

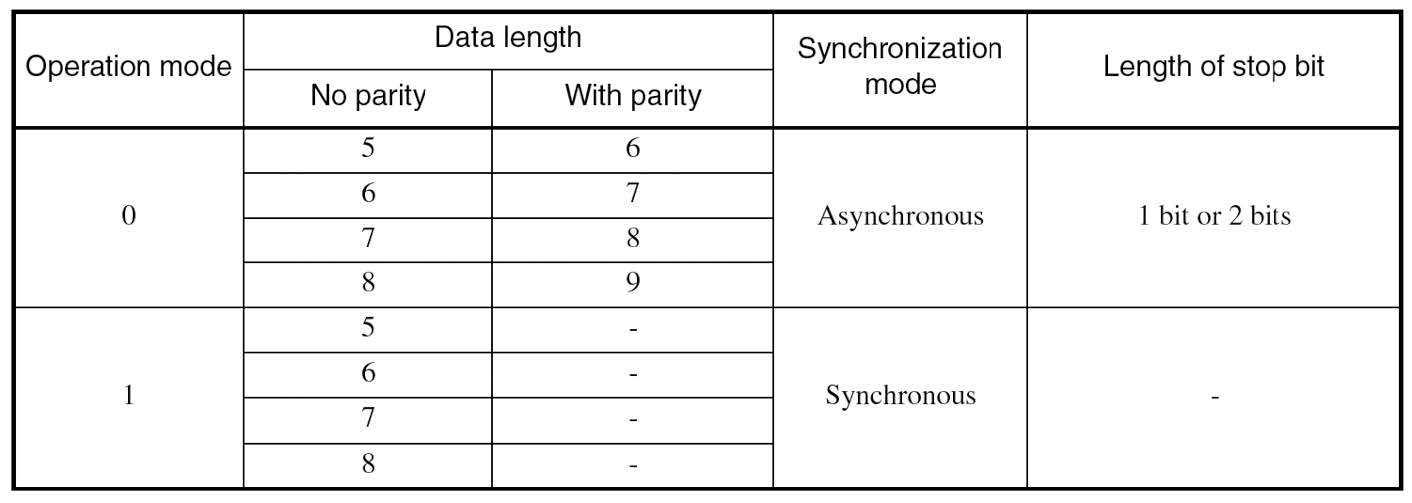

La figura 1 mette in evidenza, in maniera abbastanza schematica, i diversi modi operativi che il componente offre. Come vediamo, la figura evidenzia il modo UAR T (modo 0) con clock asincrono, mentre è usato un clock sincrono nella configurazione SIO (modo 1).

Figura 1: le modalità operative del componente.

È possibile raggruppare, sommariamente, le diverse possibilità offerte dal modulo UART/SIO del componente in questo piccolo schema:

» per il trasferimento dei dati si utilizza il protocollo NRZ (Non-Return-to-Zero);

» il chip permette il trasferimento full-duplex attraverso un doppio buffer, in questo modo è possibile garantire comunicazioni full-duplex su due canali;

» il componente permette di selezionare differenti baud rate ricorrendo ad un baud rate generator;

» è possibile selezionare differenti data frame (da 5 a 8 bit) nel caso che si opti per una configurazione senza bit di parità, mentre, in caso contrario, da 6 a 9 bit.

Diagramma funzionale del chip

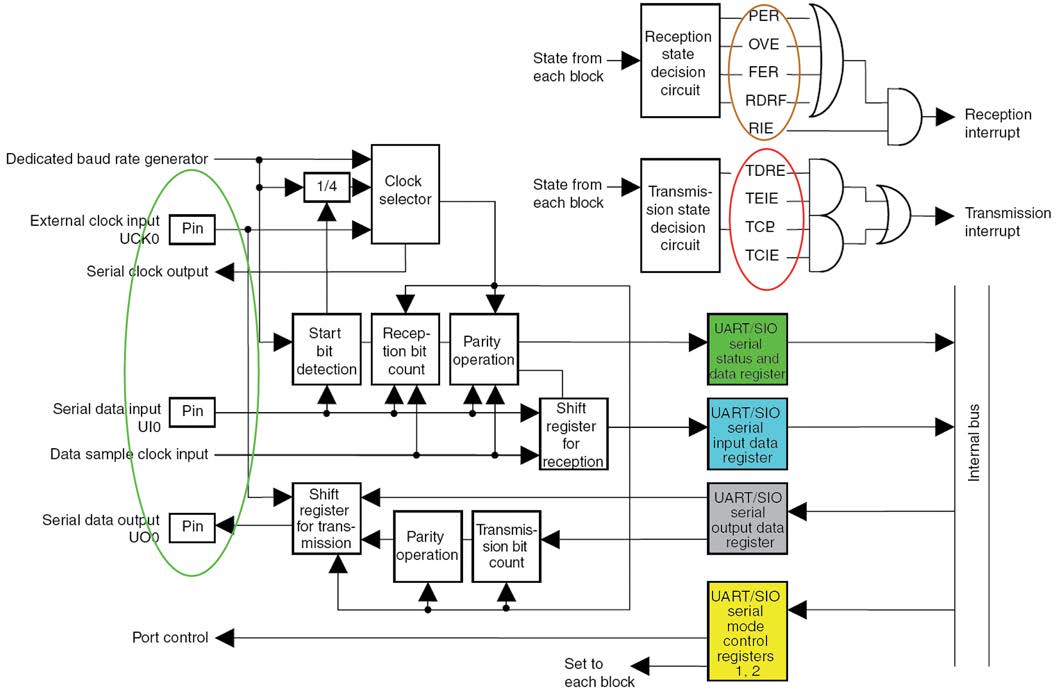

La figura 2 mostra le relazioni funzionali con i vari blocchi presenti nella sezione UART/SIO.

Figura 2: schema a blocchi della sezione SIO.

Dalla figura è possibile mettere in evidenza i seguenti registri:

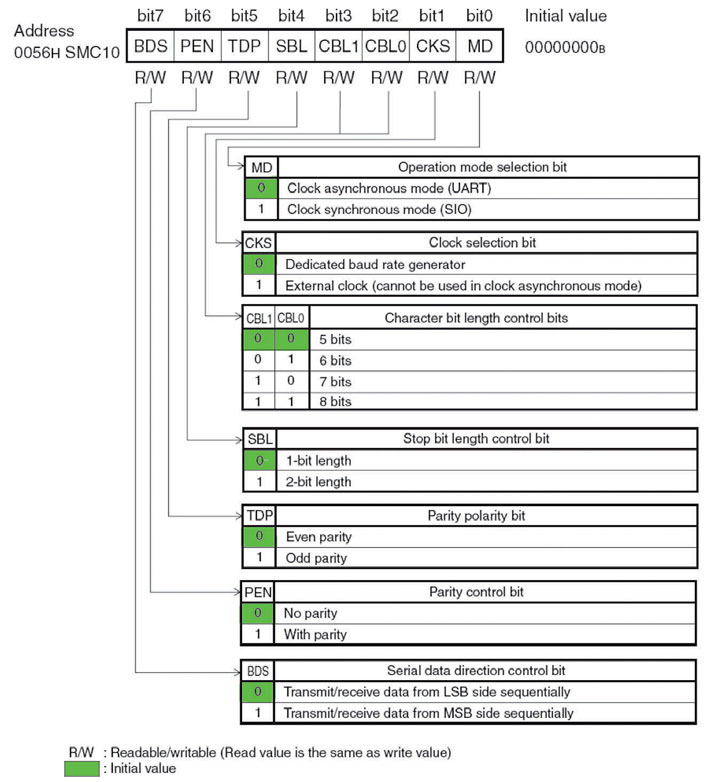

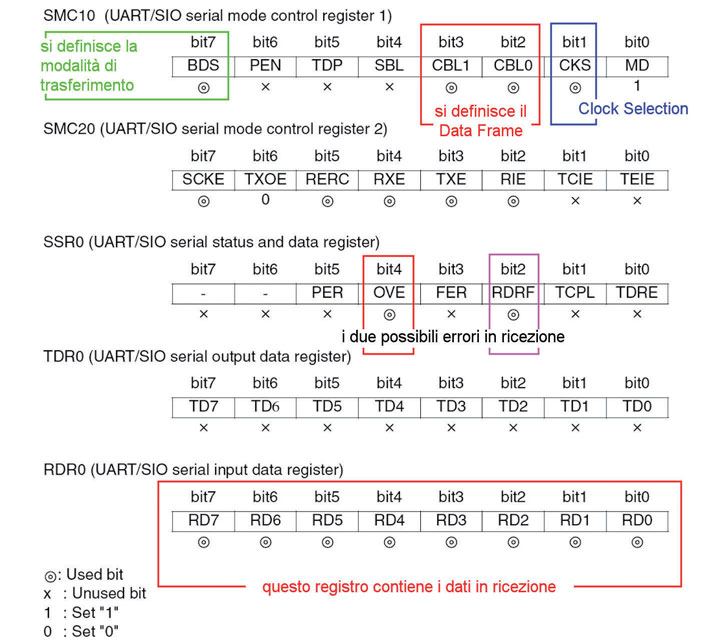

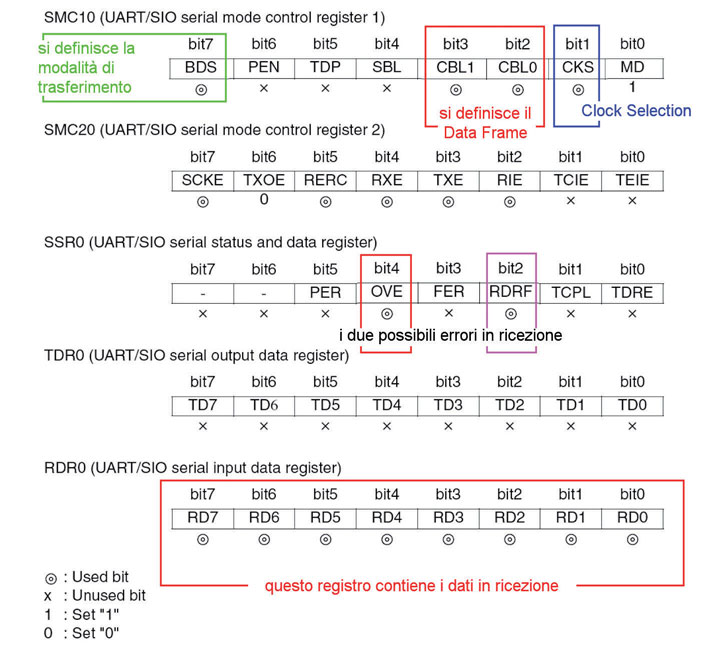

» il registro SMC10, identificato come Serial Mode Control Register 1, è di colore giallo. Questo registro permette di controllare i differenti modi operativi; cioè è possibile definire l’endianità dei dati, controllare la parità, il bit di stop, la selezione delle modalità sincrone/asincrone, la lunghezza del data frame e, per ultimo, il clock. La figura 4 mostra lo schema di questo registro con una descrizione dei vari bit, il suo indirizzo e il valore al reset;

Figura 4: il registro SMC10.

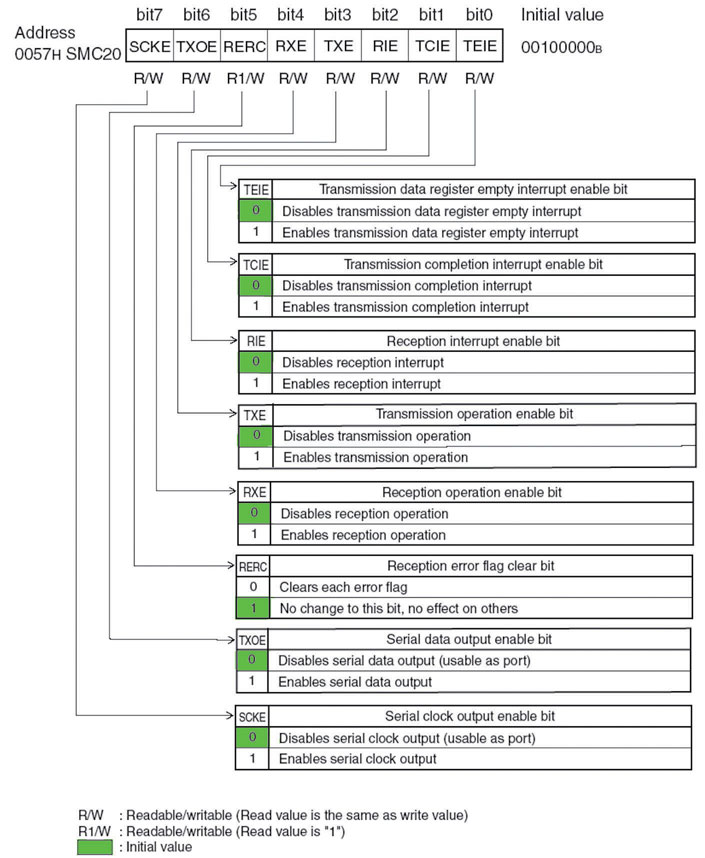

» il registro SMC20, Serial Mode Control Register 2, sempre in giallo. Questo è complementare al registro SMC10; infatti, è attraverso questo registro che è possibile abilitare o disabilitare la ricezione o la trasmissione, lo SDO, serial data output, SCO, serial clock output. È, inoltre, per mezzo di questo registro che si resettano i vari flag in ricezione. Per maggiori ragguagli si veda la figura 5 che mostra un dettaglio maggiore;

Figura 5: il registro SM20.

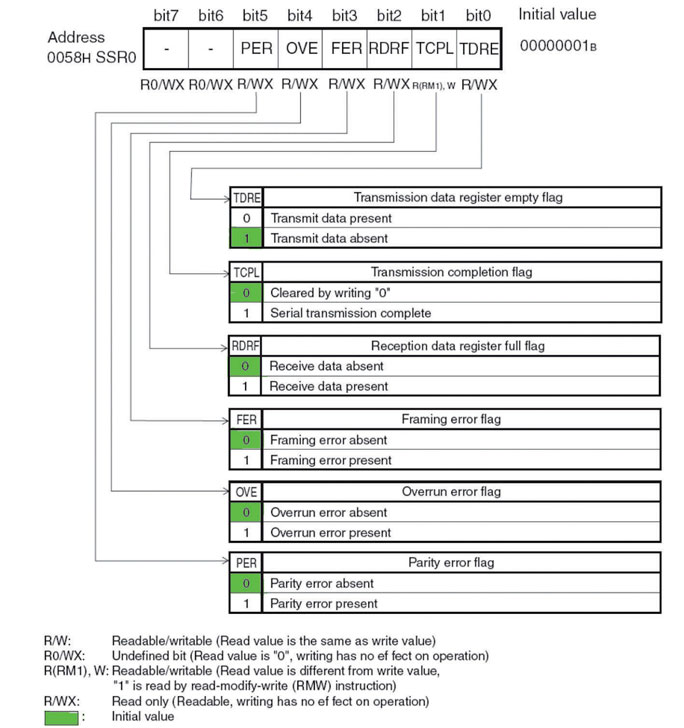

» il registro SSR0, Serial Status and Data Register, di colore verde. In questo registro trovano spazio le varie indicazioni o status in ricezione o trasmissione con i relativi status d’errore. La figura 6 mette in evidenza le sue caratteristiche interne;

Figura 6: il registro SSR0.

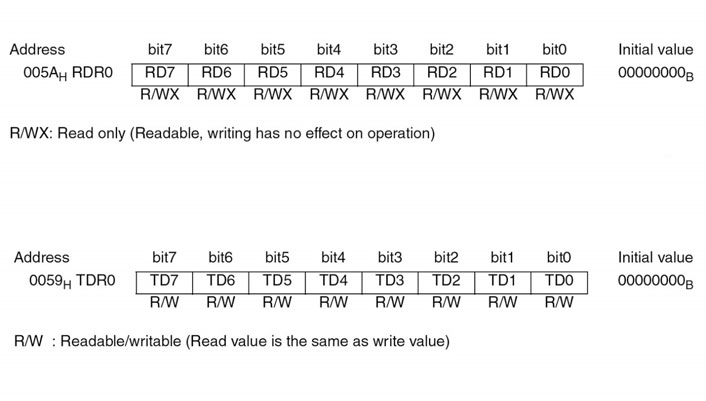

» il registro RDR0, Serial Input Data Register, è invece di colore azzurro. In questo registro trova posto il frame dei dati ricevuti in ingresso.;

» infine, il registro TDR0, Serial Output Data Register, di colore grigio. I dati scritti in questo registro sono inviati esternamente dopo le opportune conversioni interne. La figura 7 pone in evidenza i contenuti interni dei registri RDR0 e TDR0.

Figura 7: i contenuti dei registri RDR0 e TDR0

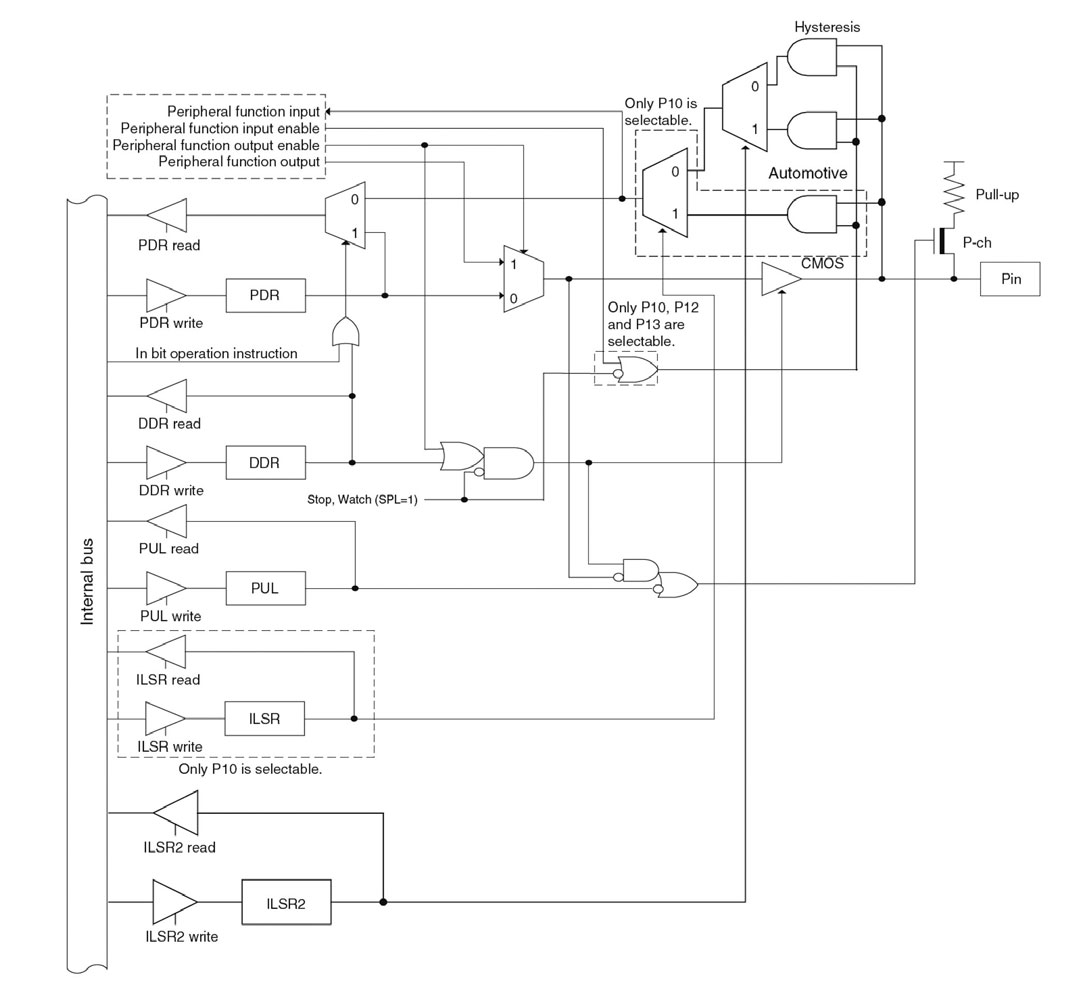

Il cerchio di colore rosso mette in risalto la sezione del blocco funzionale deputata alla gestione degli eventi asincroni, mentre quello di colore marrone si occupa degli errori. Il cerchio di colore verde mostra le connessioni tra i pin di uscita/ingresso e questo blocco funzionale, la figura 3 mette in evidenza,con un esploso abbastanza esaustivo, le relazioni tra questi pin.

Figura 3: lo stadio di ingresso.

La gestione degli interrupt

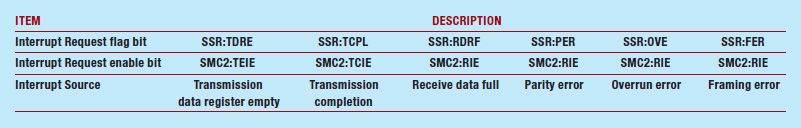

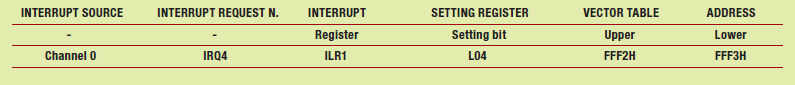

La tabella 1 mostra le differenti sorgenti di interrupt che il componente è in grado di gestire.

Tabella 1: Interrupt Control Bits & Interrupt Sourcer

Dalla tabella notiamo che il componente ha sei differenti sorgenti di interrupt associati a dei bit dedicati:

» error flag bit, comprendenti i bit PER, OVE, FER. Questi tre bit indicano errori di overrun, parity e framing e sono utilizzati come diagnostici del sistema;

» receive data register full bit, RDRF. Quando il dato è ricevuto correttamente allora il bit RDRF è posto ad un valore logico 1. In questo caso si suppone che l’intero data frame è stato processato ed è considerato corretto, cioè il dato è stato ricevuto fino al bit di stop. Questo flag assume il significato di fine frame;

» transmission data register empty bit, TDRE. L’uso di questo bit è abbastanza intuitivo, infatti è attraverso questo bit che si determina quando il componente è pronto a ricevere un successivo frame;

» transmission completion flag, TCPL. Questo indica la fine della trasmissione di un data frame.

La tabella 2, invece, pone in evidenza i registri e i vettori utilizzati durante la gestione di una ISR associata. Per permettere la gestione di questi interrupt è necessario abilitare il bit RIE del registro SMC2.

Tabella 2 – Registers and Vector Table Related to UART/SIO Interrupts

Modalità sincrona

Come si è scritto, il componente è in grado di funzionare nelle due modalità previste, asincrona o sincrona. Questa possibilità si concretizza attraverso la programmazione dei relativi registri. Il registro SMC10, e nella fattispecie, il bit MD, vedi figura 4, è utilizzato per definire la modalità di funzionamento. In questo caso, se si vuole configurarlo in modalità sincrona occorrerà scrivere un valore logico 1. Successivamente, il clock è definito utilizzando il registro SMC10, bit CKS. Il data frame, nella modalità sincrona (SIO), è variabile tra 5 e 8 bits; in ogni caso, è necessario considerare che,in questa modalità, la parità è disabilitata e nessuno stop bit è utilizzato.

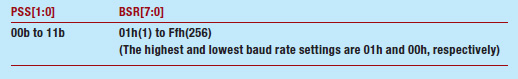

Il valore del baud rate deve essere scelto secondo quanto stabilito dalla tabella 3.

Tabella 3: Baud Rate Setting Range in SIO Mode

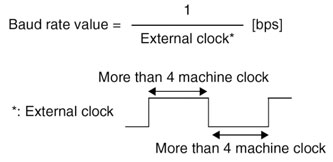

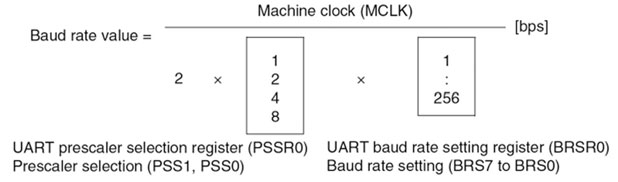

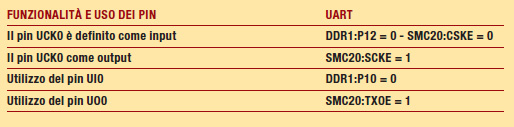

Le figure 8 e 9 illustrano le relazioni utilizzate per ottenere il baud rate quando è applicato o un clock esterno o un generatore di baud Infine, è necessario definire il comportamento dei vari pin del blocco UART/SIO, tabella 4.

Figura 8: le relazioni usate per determinare il baudrate

con clock esterno.

Figura 9: le relazioni usate per determinare il baudrate con generatore di baudrate.

Tabella 4: UCK0, UI0, UO0

La ricezione secondo la modalità sincrona

La comportamento in ricezione del componente dipende dal tipo di clock utilizzato: interno piuttosto che esterno. In caso, per esempio, di clock esterno con l’abilitazione all’uscita dei dati (RXE), il data frame è processato sempre sul fronte di salita del clock. Viceversa, in caso di segnale interno, il clock in uscita è in relazione con la trasmissione. Quando un data frame è pronto per essere letto, cioè è uscito precedentemente dal registro interno reception shift, allo questo risulta essere presente nel registro RDR0. Il progettista software viene avvisato dalla circuiteria hardware mediante il valore appropriato del bit RDRF. La lettura di questo registro resetta, in maniera trasparente e automatica, il bit RDRF, di conseguenza, in questo modo il componente è abilitato ad una nuova ricezione. Per aumentare in flessibilità è possibile associare un evento asincrono ad ogni buffer pieno, in questo modo si evita di andare a controllare, ad un intervallo di tempo stabilito, il flag RDRF. Per fare questo è necessario abilitare gli interrupt mediante il bit RIE. In questo modo, ogni volta che il buffer risulta pieno (RDRF=1) e gli interrupt risultano abilitati (RIE=1), il componente solleverà un interrupt interno che il software dovrà gestire. Del registro SMC20 (UAR T/SIO serial mode control register 2) si utilizzano solo i bit previsti nella modalità SIO, in questo modo:

» bit RERC, è utilizzato per azzerare i vari error flag presenti. Con la scrittura di un valore logico “0” si resettano gli error flag in ricezione;

» bit TXOE e bit SCKE. L’uso di questi bit sono utili per definire, e relazionare, tra loro i vari pin presenti sul chip. In ricezione sono possibili due differenti eventi asincroni, il caso di buffer di ricezione pieno e l’errore di overrun (OVE). Quando si presenta un errore di tipo OVE, i dati non sono trasferiti verso il registro RDR0. La figura 10 mette in evidenza i vari registri utilizzati per programmare il componente in modalità SIO.

Figura 10: i registri per programmare il componente in modalità SIO.

Per analogia, la figura 11 mette in evidenza i vari registri coinvolti per inizializzare e gestire la stessa modalità in trasmissione.

Figura 11: I registri coinvolti per inizializzare e gestire la modalità SIO in trasmissione