Con l’incredibile evoluzione che negli ultimi anni ha avuto il mondo di internet, un numero sempre maggiore di applicazioni industriali, consumer o addirittura medicali hanno la necessità di avere una interfaccia verso la grande Rete Mondiale. Microchip ha realizzato tempo fa un Front End in grado di interfacciare in maniera semplice e robusta una qualsiasi applicazione ad una rete Ethernet o TCP-IP: il componente è l’ENC28J60.

Introduzione

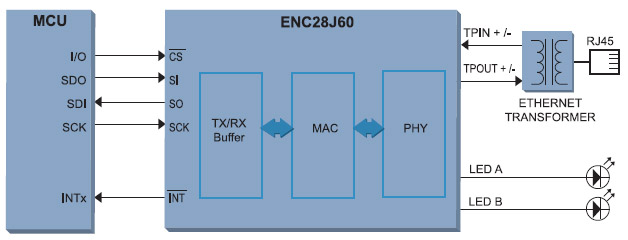

L’ENC28J60 è un dispositivo dotato di 28 pin, in grado di interfacciare un qualsiasi microcontrollore o sistema dotato di una porta SPI ad una interfaccia IEEE 802.3 con un data rate di 10 Mbit/sec. Come appare in figura 1, lo schema a blocchi di un sistema basato sul componente in esame è davvero semplice.

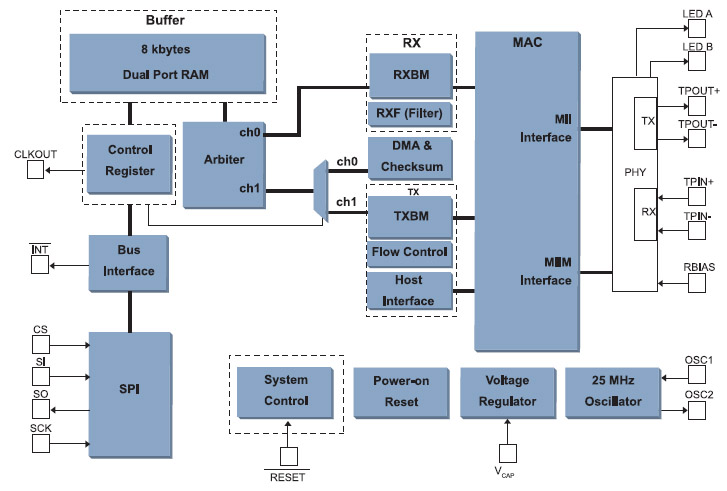

Si può vedere che un microcontrollore dotato di porta SPI utilizza una comunicazione seriale sincrona completa (dato in ingresso, dato in uscita, clock, chip select e interrupt di buffer pieno). Scendendo nel dettaglio, è possibile scindere il dispositivo in 7 blocchi di funzionamento distinti: il citato blocco SPI, i registri di controllo utilizzati per programmare il funzionamento del device, una Dual Port RAM per bufferizzare i dati in ingresso e in uscita, un blocco di arbitraggio per la protezione da scrittura contemporanea sui registri della Dual Port, una interfaccia a bus che funge da interprete comandi per i dati e i comandi in ingresso dalla porta SPI, l’importantissimo blocco MAC, che assicura il corretto funzionamento del dispositivo secondo la normativa 802.3 ed infine il PHY, il layer fisico che codifica e decodifica i dati presenti sul bus ethernet e li rende interpretabili digitalmente dalla logica del dispositivo. In figura 2 si propone uno schema che riassume i blocchi sopra citati.

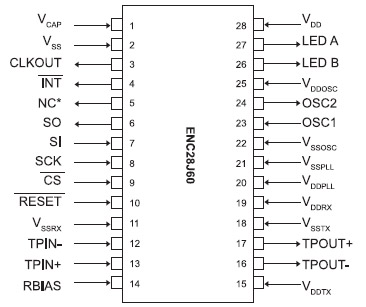

Per le considerazioni che seguiranno nell’articolo, sottoponiamo all’attenzione del lettore anche il pinout del dispositivo, che come detto è un 28 pin, disponibile in ben 4 case: il Dual In Line, il SOIC28, il SSOP28 e infine il compatto QFN28 (6mm per 6mm).

INTERFACCIAMENTO E CONFIGURAZIONE DI MEMORIA DEL DISPOSITIVO

Componenti esterni per creare l’interfaccia Ethernet

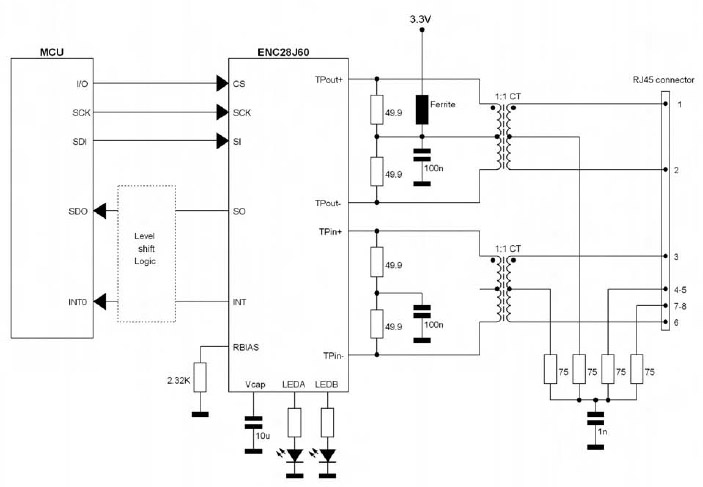

Nell’analisi di un dispositivo operante su Ethernet come ENC28J60 spicca immediatamente l’elevatissimo livello di integrazione raggiunto: pochissimi sono infatti i componenti da affiancare all'ENC28J60 per renderlo operativo nella realizzazione dell’interfaccia di rete. Come ogni dispositivo operante su bus Ethernet, il ENC28J60 lavora a 25MHz, che possono essere forniti da un normalissimo quarzo oppure da un oscillatore, secondo le preferenze dell’utente finale. Oltre all’oscillatore, il componente richiede un resistore esterno da 2,32KOhm, precisione 1%, da porre fra il pin 14 e GND, che regola l’amplificazione dello stadio di uscita del dispositivo. L’ENC28J60 opera ad una tensione nominale di 3,3Vdc, ma il core ha alcune parti che lavora a 2,5Vdc. Internamente al componente esiste un regolatore di tensione, che però richiede un condensatore esterno, del valore compreso fra 1mF e 10mF, da porsi fra il pin 1 e GND. Il bus ethernet, così come avviene nella maggioranza dei casi di comunicazione a bus, lavora in maniera isolata dalle board connesse, quindi anche ENC28J60 si attende un trasformatore di isolamento 1:1 sullo stadio di uscita e sullo stadio di ingresso. Fra il componente e il trasformatore può essere inserita una rete di disaccoppiamento, formata da due resistori da 49,9 Ohm1% uniti ad un induttore ed un condensatore di valori opportuni al raggiungimento dell’immunità desiderata. All’uscita del trasformatore andrà invece connesso il connettore di tipo RJ45, standard delle connessioni di rete. Questi connettori alloggiano abitualmente due Led, che nello standard sono denominati “Link” ed “Act”, ossia “connessione presente” ed “attività presente” sul bus. L’ENC28J60 è dotato di due pin espressamente dedicati al pilotaggio di questi due led (pin 26 e 27). Queste connessioni sono efficacemente raccolte in uno schema a blocchi, presentato in figura 4.

Organizzazione della memoria

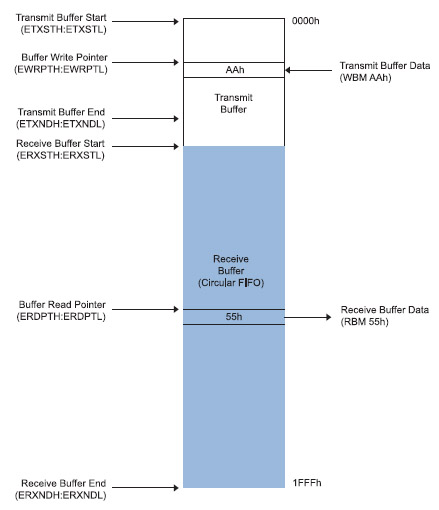

Come anticipato, la memoria del dispositivo può essere suddivisa in tre grandi sezioni: i registri di controllo, i buffer Ethernet ed i registri per il Physical Layer. I registri di controllo sono chiaramente usati per configurare il funzionamento del dispositivo e sono controllati direttamente dalla porta SPI, quindi dal microcontrollore esterno che colloquia appunto su seriale sincrona. Uno dei comandi più interessanti è il SRC (System Reset Command), che consente di effettuare un Soft Reset del dispositivo Il buffer Ethernet, invece, è una FIFO utilizzata dal controller Ethernet per bufferizzare i dati in ingresso e in uscita. Questa memoria ha una densità totale di 8kbyte e lo sharing fra buffer tx e buffer rx può essere programmato da utente attraverso SPI, tramite il settaggio degli stack buffer pointers ERXSTH:ERXSTL e ERXNDH:ERXNDL, che limitano il buffer di ricezione; la parte rimanente (ossia gli 8kbyte meno quanto dedicato alla ricezione) vengono automaticamente destinati alla trasmissione. Il puntatore a questo stack di memoria è gestito autonomamente ed automaticamente dall’hardware del dispositivo, ragion per cui l’utente non deve fare altro che attendere l’opportuno Interrupt di Stack Full per ricevere i dati. Ciononostante, il buffer pointer può essere letto da SPI, in modo da tenere sempre “sotto controllo” il livello dello stack ed eventualmente provvedere a liberare memoria nei omenti in cui il sistema è scarico di lavoro. In figura 5 si presenta un esempio di struttura della memoria Ethernet.

Per finire, i PHY registers consentono di controllare il Physical Layer del dispositivo: si tratta quindi di 9 registri a 16 bit, simili ai control register, ma espressamente dedicati al layer di interfaccia fisica ethernet del dispositivo.

IL PROTOCOLLO ETHERNET IEEE 802.3 IN UN ENC28J60

Struttura di un pacchetto

In ogni sistema di comunicazione, la comprensione e l’ottimizzazione del sistema è legata alla conoscenza del pacchetto: dei suoi componenti, della sua struttura, dei controlli e della lunghezza totale che questo pacchetto ha in bit. Nel caso dello standard IEE 302.3, si ha inizialmente un preambolo di 7 byte (che serve a “risvegliare” il dispositivo in ascolto, eventualmente in attesa o in sleep mode) e di un byte SOF (Start Of Frame). Questi bit, non portando contenuto informativo, vengono filtrati dal modulo ricevente, che può essere il nostro ENC28J60 o un modulo Ethernet a cui il nostro device sta comunicando. A questi seguono 6 byte per indicare l’indirizzo MAC del destinatario del messaggio. Ogni messaggio può essere destinato a un solo destinatario, ad un gruppo preciso di destinatari o a tutti i componenti della rete: si parla rispettivamente di Unicast, Multicast o Broadcast. A questi seguono ulteriori 6 byte, che identificano questa volta l’indirizzo MAC di chi invia il messaggio. Seguono poi due bit che indicano la lunghezza del pacchetto o il tipo di pacchetto (comando o dato). Per finire, si ha il vero e proprio dato, che può avere lunghezza compresa nell’intervallo 46…1500 bytes. Se il messaggio ha lunghezza inferiore ai 46 byte, allora in automatico il dispositivo genera un filling dei bytes necessari (padding). Al termine del payload, si trovano 4 bytes di CRC, che viene calcolato sulla base di tutto il pacchetto, ad eccezione del preambolo e del SOF. In figura 6 una immagine con la struttura di un pacchetto 802.3.

UNICAST, MULTICAST E BROADCAST

Il criterio scelto per discriminare fra i tre citati tipi di destinazione dell’informazione sta nel bit meno significativo del primo byte del MAC del destinatario. Se questo bit è ad uno, allora si tratta di una trasmissione Multicast o Broadcast, altrimenti si tratta di una Unicast. Distinguere poi fra una trasmissione Multicast ed una Broadcast è davvero semplice, dal momento che un messaggio Broadcast ha come registro MAC del destinatario l’indirizzo protetto FF-FF-FF-FF-FF-FF. Da notare che, convertendo questo valore esadecimale in numero binario, si ottengono tutti 1, ed in particolare si ottiene 1 al bit meno significativo del primo byte.

Filtri in ricezione

Altra caratteristica davvero interessante del dispositivo è la possibilità di filtrare i messaggi in arrivo, decidendo di “leggere” effettivamente solo quelli che rispondano a certi criteri, similmente a quanto avviene nel CAN bus o in altri standard di comunicazione basati sul messaggio piuttosto che sugli indirizzi. Per quanto concerne il nostro ENC28J60, è possibile settare 6 diversi tipi di filtro. Il primo è chiamato Filtro Unicast e, molto semplicemente, consiste nell’abilitare la ricezione dei soli messaggi il cui Destination MAC Address sia quello del ENC stesso. Il secondo filtro è detto Pattern Match Filter e consiste nel confronto del CRC del messaggio in arrivo con valori di CRC impostati a priori: in questo modo è possibile ricevere solo messaggi i cui dati siano stati anzitempo “approvati” e accettati. Il terzo è detto Magic Racket Filter e consiste in un filtraggio dell’indirizzo del destinatario, come per l’Unicast Filter, e nel check di tutto il Data Pattern, alla ricerca di una “Sequenza Magica”. Solo in presenza di questa sequenza di dati precisi il pacchetto verrà accettato: com’è facile intuire, un sistema di filtraggio del genere può essere utile nei casi in cui lo scambio di dati debba esser consentito solo da mittenti accreditati, per ragioni di sicurezza. Il quarto è detto Filtraggio della Hash Table. Questo filtro consiste nel confronto fra il risultato di un CRC effettuato sui 6 byte di indirizzo del destinatario con il corrispondente bit presente nel registro EHT del dispositivo. Ad esempio, se il valore del CRC è 6, si andrà a vedere se il bit numero 6 di EHT è settato. Solo in tal caso il messaggio verrà ricevuto. Per finire, gli ultimi due filtri sono detti Multicast Filter e Broadcast Filter e, chiaramente, consentiranno di ricevere solo pacchetti che abbiano la caratteristica di essere Multicast o Broadcast.

Duplex

Come in ogni sistema di comunicazione dati, anche in Ethernet vi è la possibilità, in un dato istante di tempo, di ricevere solamente o trasmettere solamente (Half Duplex) oppure di poter contemporaneamente tra smettere e ricevere dati (Full Duplex). In questo secondo tipo di comunicazione, se il nostro ENC28J60 è in trasmissione, al termine di ogni pacchetto di dati verranno inseriti dei tempi di attesa, detti Pause Control Frames, previsti dal protocollo IEEE 802.3. Questi tempi sono realizzati tramite l’invio di 64 bytes di dato cui viene associato un indirizzo di destinazione multicast riservato, in modo da consentire l’eventuale ricezione di pacchetti in arrivo.

Questo controller fa il paio con un altro molto diffuso, l’MCP2515, CAN controller con interfaccia SPI. Chiaramente molto piu’ “semplice” rispetto a un controller Ethernet, visto la netta diversita’ fra i 2 bus.

Qualche anno fà ho realizzato un progetto di web server con un analogo modulo, il modulo WIZ811MJ della Wiznet basato sul chip W5100. Di seguito vi riporto le interessanti caratteristiche di questo modulo:

CARATTERISTICHE TECNICHE:

TCP/IP, MAC protocol layer: W5100

Physical layer: Included in W5100

Connector: MAG-JACK (RJ45 with Transformer)

Supports 10/100 Base TX

Supports half/full duplex operation

Supports auto-negotiation and auto cross-over detection

IEEE 802.3/802.3u Compliance

Operates 3.3V with 5V I/O signal tolerance

Supports network status indicator LEDs

Includes Hardware Internet protocols: TCP, IP Ver.4, UDP, ICMP, ARP, PPPoE, IGMP

Includes Hardware Ethernet protocols: DLC, MAC

Supports 4 independent connections simultaneously

Supports MCU bus Interface and SPI Interface

Supports Direct/Indirect mode bus access

Supports Socket API for easy application programming

Chi fosse interessato al progetto può trovarlo nel mio blog.

Ciao Fulvio,

non conoscevo il tuo blog, ci sono cose molto interessanti. Sto giusto guardando ora il progetto col web server.

Grazie Riccardo.