Come realizzare un’applicazione ultra low-power con ricezione radio intermittente con il micro CC430 di Texas Instruments.

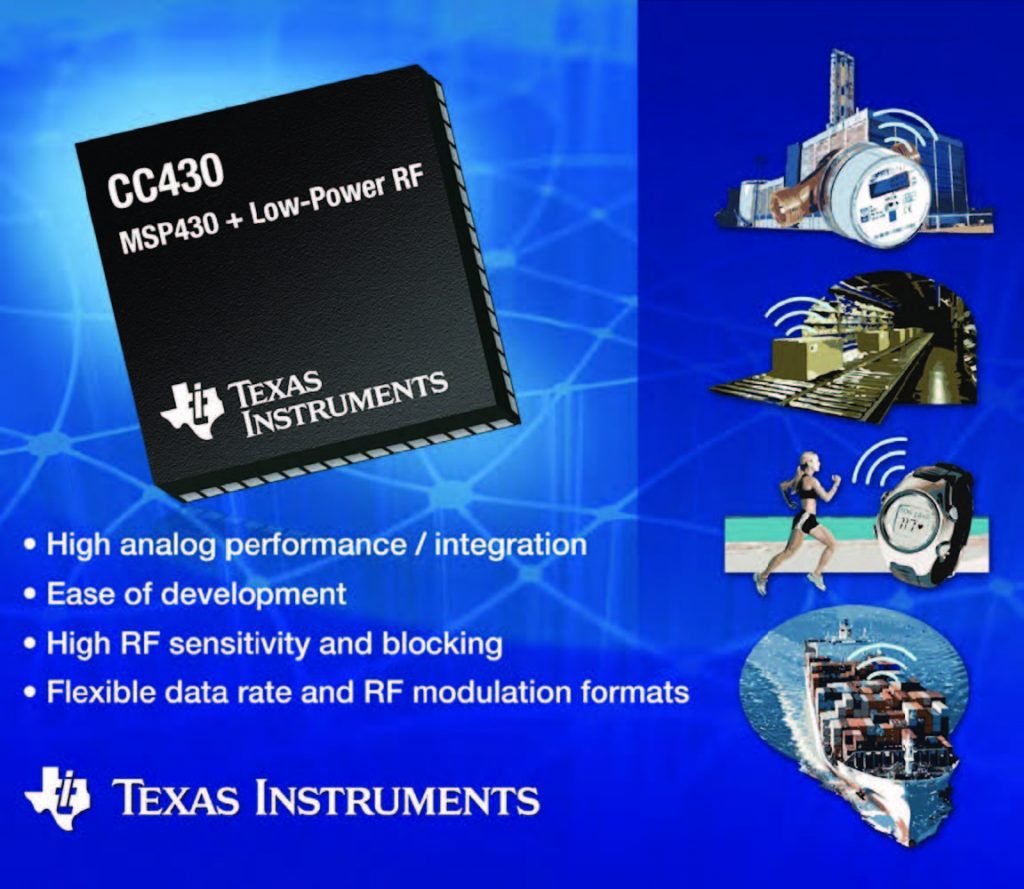

CC430 è la famiglia di microcontrollori a 16-bit di Texas Instrument per il mercato delle applicazioni wireless low power in ambito, ad esempio, di sicurezza personale, building automation o metering. I dispositivi (figura 1) integrano CPU MPS430X con architettura RISC e, insieme, di istruzioni ortogonali, moltiplicatore hardware a 32-bit, controller flash/RAM, acceleratore AES, convertitore A/D SAR a 12-bit, controller LCD a 96 segmenti, porta di comunicazione compatibile con i protocolli UART/SPI/I2C e modulo radio RF1A. Di seguito è descritta, in particolare, la modalità Wake On Radio di tale periferica.

Il modulo RF1A

Il modulo radio RF1A è basato sul core CC1101 (figura 2) che implementa un ricevitore a frequenza intermedia (IF) mediante amplificatore LNA (Low-Noise Amplifier), down-converter e conversione A/D delle componenti in quadratura; controllo di guadagno automatico, filtro di canale fine, demodulazione e sincronizzazione sono, quindi, eseguiti nel dominio digitale.

Figura 1: i micro CC430 di TI con periferica radio

Il trasmettitore integra modulatore e sintetizzatore di frequenza con VCO (Voltage Controllerd Oscilattor) on-chip e phase shifter di 90°. Memorie fifo in trasmissione e ricezione assicurano, infine, adeguata capacità di buffering locale nella comunicazione con la CPU.

![Figura 2: architettura del modulo radio RF1A (da [1])](https://it.emcelettronica.com/wp-content/uploads/2019/08/architettura-del-modulo-radio-RF1A-da-1-1024x647.jpg)

Figura 2: architettura del modulo radio RF1A (da [1])

- supporto per le bande tra 300 MHz e 348 MHz, tra 389 MHz e 464 MHz e 779 MHz e 928 MHz;

- supporto per le modulazioni 2-FSK, 2GSK, MSK, OOK ed ASK;

- data rate programmabile da 0,8 kBaud a 500 kBaud;

- elevata sensibilità in ricezione (-110 dBm con data-rate di 2 kBaud a 868 MHz, percentuale di errore di pacchetto dell’1%);

- potenza di uscita programmabile;

- supporto on-chip per riconoscimento di sync, controllo e generazione automatica di CRC;

- wake on radio

La periferica è controllabile direttamente dalla CPU mediante registri. La comunicazione è basata su canali logici; ad ogni istruzione inviata corrisponde una risposta di stato come pure ad ogni dato scritto/letto. Alcune istruzioni prevedono risposte ‘dummy’ per le quali è supportata un modalità di autoread per ridurre il carico della CPU nella gestione della periferica. È implementata una macchina a stati interna per la commutazione tra i diversi modi operativi mediante comando o a seguito di eventi (overflow, ad esempio, della fifo di trasmissione).

Il Timer Wake On Radio

Tale macchina a stati include in particolare uno stato di SLEEP in cui la periferica è disabilitata per ridurre la dissipazione di potenza dinamica del microcontrollore. Il dispositivo entra in tale modalità mediante comando specifico. È quindi previsto un timer Wake On Radio che consente di attivare automaticamente ad intervalli periodici la periferica, con intervento minimo da parte della CPU, per la ricezione di pacchetti. La funzionalità deve essere abilitata espressamente prima di forzare il modulo radio in SLEEP. Il timer Wake On Radio, come mostrato schematicamente in figura 3, include due eventi, denominati Event0 ed Event1. Il primo determina l’asserzione di interruzioni periodiche alla CPU, in risposta alla quale è richiesto che questa riporti la periferica RF1A nello stato di IDLE mediante apposito comando.

![Figura 3: la sequenza di eventi della modalità Wake On Radio (da [1]).](https://it.emcelettronica.com/wp-content/uploads/2019/08/la-sequenza-di-eventi-della-modalità-wake-on-radio.jpg)

Figura 3: la sequenza di eventi della modalità Wake On Radio (da [1]).

Software di esempio

La figura 4 mostra uno schema di principio del flusso logico nella gestione della funzionalità Wake On Radio del CC430, come descritto nell’Application Note SLAA459 “CC430 Wake On Radio Functionality” di Texas Instrument.

![Figura 4: diagramma di flusso per la gestione della modalità Wake On Radio (da [2]).](https://it.emcelettronica.com/wp-content/uploads/2019/08/Firmware-68-1024x497.jpg)

Figura 4: diagramma di flusso per la gestione della modalità Wake On Radio (da [2]).

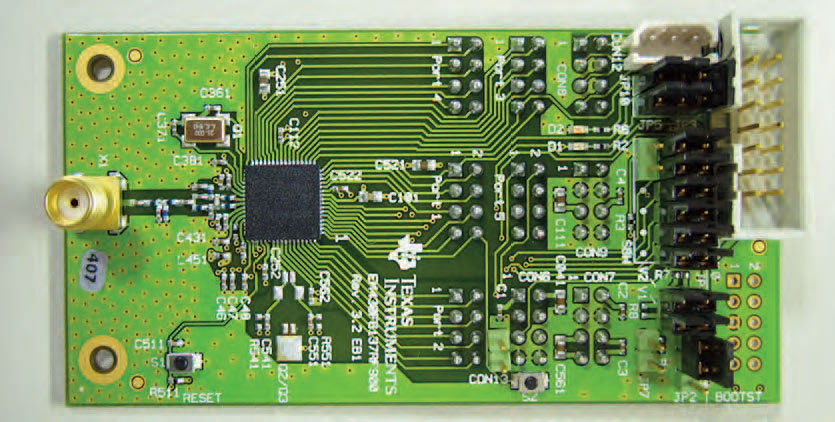

Figura 5: la scheda di sviluppo EM430F6137R F900 per CC430.

Come si vede dal diagramma di flusso di figura 4, dopo aver configurato la periferica, la CPU attiva la modalità Wake On Radio ed entra in uno degli stati low-power previsti. Viene risvegliata da questa mediante interruzione. Un Interrupt Handler software determina quindi la sorgente attiva ed esegue le corrispondenti operazioni prima di riportare la CPU nella particolare modalità low-power stabilita dalla applicazione. Nel caso in particolare di interruzione per Event0, la CPU abilitata le interruzioni del core RF1A relative alla ricezione di pacchetti o allo spegnimento dell’LNA e quindi attende 850 µs prima di forzare l’RF1A in IDLE. Tale attesa è necessaria per assicurare che l’oscillatore radio si stabilizzi; prima di ciò, eventuali accessi ai registri di controllo e configurazione della periferica sono non validi. Il listato 1 riporta una possibile implementazione della funzione di inizializzazione ed attivazione della funzionalità Wake On Radio, come è inclusa nell’esempio discusso nell’Application Note SLAA459 citata in precedenza.

void RfModeWOR(void) //Sets up the RF1A in WOR mode and puts the CPU

core in LPM3 mode.

{

WriteSingleReg(WOREVT1, 0x87);

WriteSingleReg(WOREVT0, 0x6B);

WriteSingleReg(MCSM2, 0x00);

WriteSingleReg(WORCTRL, (7 << 4) | 0);

WriteSingleReg(IOCFG1, 0x29); // GDO1 = RF_RDY

while (1)

{

Strobe(RF_SWOR);

wor = 1;

RF1AIE |= ( (BIT6) << 8 ); // BIT14 = BIT6 << 8

__bis_SR_register(LPM3_bits + GIE);

}

}

| Listato 1 |

Il registro WORCTRL configura la modalità Wake On Radio. Il campo WORCTRL[1:0] definisce in particolare il valore WOR_RES che controlla la risoluzione dell’ Event0, come pure i timeout massimi per gli eventi di Wake On Radio e funzionamento normale in ricezione. Il campo WORCTRL[6:4] imposta invece il timer per l’Event1 selezionando uno tra 8 possibili valori compresi tra 4 e 48 cicli di clock, corrispondenti a 0,122 ms e 1,465 ms rispettivamente ad una frequenza del clock ausiliario del microcontrollore di 32 KHz. Il campo WORCTRL[7] consente infine di abilitare appunto (scrivendovi ‘0’) la modalità Wake On Radio del modulo. I registri WOREVT0 e WOREVT1 definiscono poi il valore del campo Event0 secondo la seguente relazione: tEvent0= 1/fACLK × Event0 × 255xWOR_RES mentre il registro MCSM2 imposta la durata dell’intervallo in cui l’RF1A è nello stato RX. Nel caso particolare dell’esempio riportato nel listato 1, il registro WORCTRL viene configurato impostando un timeout massimo di 2 s con risoluzione di 1 periodo di clock per l’Event0, una durata di 12 cicli per l’Event1. Il programma forza quindi il modulo RF1A in SLEEP (riga 10), abilita la relativa interruzione (riga 12) e attiva la modalità LPM3 (riga 13). Il listato 2 mostra, invece, l’esempio per l’implementazione dell’Interrupt Handler per la corretta gestione della modalità Wake On Radio.

v#pragma vector=CC1101_VECTOR

__interrupt void CC1101_ISR(void)

{

switch(__even_in_range(RF1AIV,32))

// Prioritizing Radio Core Interrupt

{

case 4:

// GDO1 = LNA_PD signal

RF1AIE &= ~(BIT1+BIT9);

Strobe(RF_SWOR);

// Go back to sleep

break;

case 20:

// RFIFG9

if (!transmitting)

// RX end of packet

{

RF1AIE &= ~(BIT1+BIT9);

RxBufferLength = ReadSingleReg( RXBYTES );

// Read the length byte from the FIFO

ReadBurstReg(RF_RXFIFORD, RxBuffer, RxBufferLength);

}

else

// TX end of packet

RF1AIE &= ~BIT9; // Disable TX end-of-packet interrupt

__bic_SR_register_on_exit(LPM3_bits);

break;

case 30: // WOR_EVENT0

RF1AIE |= BIT9 + BIT1;

RF1AIFG &= ~(BIT9 + BIT1);

RF1AIES |= BIT9;

// Falling edge of RFIFG9

Strobe( RF_SRX );

// Built-in 810us delay in Strobe()

break;

default: break;

}

}

| Listato 2 |

Se si vuole approfondire l’argomento, TI mette a disposizione il Software gratuito SmartRF-Studio per fare uno studio preliminare ma anche per la programmazione di un sistema di trasmissione RF LowPower. Inoltre con la scheda di sviluppo citata nell’articolo, dedicando il giusto tempo alla progettazione, si può sperimentare un sistema TX-RX a basso consumo, alimentato a batterie 2x AAA – 3Volt; leggevo 0,05W in ricezione. Non ho invece capito quale può essere il range di distanza massima raggiunta…. Applicazioni possono essere ricezione video di telecamere nascoste, sistemi di allarme wireless, oltre che sensori indossabili.

Un altro componente interessante che avevo visto qualche tempo fa, caratterizzato da bassissimi consumi è il SoC multiprotocollo di fascia alta nRF5340 della Nordic Semiconductor basato su doppio processore ARM Cortex, supporto di numerosi protocolli RF e temperatura operativa massima piuttosto estesa (105 C). Non so se in questo caso, essendo un prodotto appunto di fascia alta, i due chip siano paragonabili ma è evidente che il richiamo del mondo IoT stia guidando questo settore di mercato verso una competizione sempre più agguerrita.