Gli IC standard sono integrati costruiti senza considerare una specifica applicazione, quindi hanno una serie di funzionalità generiche che potrebbero essere in eccesso per un caso specifico cosi come potrebbero non avere una funzionalità essenziale all’applicazione stessa. Utilizzando gli IC standard è facile quindi trovarsi nella situazione di avere un eccessivo consumo di potenza, dover disabilitare componenti, dover trovare soluzioni personalizzate oppure eseguire test impegnativi.

Le logiche programmabili

La Figura 1 riporta la classificazione completa di tutte le tipologie di circuiti integrati.

Figura 1: classificazione dei circuiti integrati. A differenza di quelli standard gli IC di tipo ASIC sono creati appositamente per tipologie di applicazioni o per applicazioni ben definite

Gli ASIC (Application Specific Integrated Circuits) sono IC creati appositamente per tipologie di applicazioni oppure per applicazioni ben definite. Una prima distinzione tra circuiti di tipo ASIC si fa distinguendo circuiti full custom e circuiti ASIC semi custom. Gli ASIC full custom sono circuiti creati appositamente per soddisfare le esigenze di un’applicazione ben precisa. In questo modo si ottiene una struttura ottimizzata con buonissime prestazioni, dimensioni contenute e consumo di potenza minimizzato. Questo tipo di circuito presenta svantaggi importanti tra cui costi piuttosto elevati. Gli svantaggi dei IC full custom sono, almeno in parte, ridotti nel caso dei semi custom, dove la struttura viene creata con lo scopo di soddisfare intere categorie di applicazioni. Il chip è readyto-use e quindi i tempi di programmazione sono notevolmente ridotti. Una categoria di circuiti semi custom molto utilizzata è rappresentata dalle PLD (Programmable Logic Device). In tale tipologia rientrano:

- SPLD (Simple PLD) tra cui ROM, PAL e PLA. L’architettura SPLD è costituita da 2 matrici, una di AND e l’altra di OR che permettono l’implementazione di funzioni logiche e quindi la sintesi di reti combinatorie tramite OR di mintermini.

- CPLD (Complex PLD). I circuiti di questo tipo sono un’evoluzione delle PAL dove si fa largo uso di macrocelle. Si possono considerate come insiemi di dispositivi di tipo PAL integrati sullo stesso chip. In aggiunta è possibile programmare anche la matrice che interconnette le macrocelle.

- FPGA (Field Programmable Gate Array). Rappresentano un’evoluzione ulteriore delle CPLD dove la complessità è successivamente aumentata così come incrementatato il livello di personalizzazione.

Struttura delle FPGA

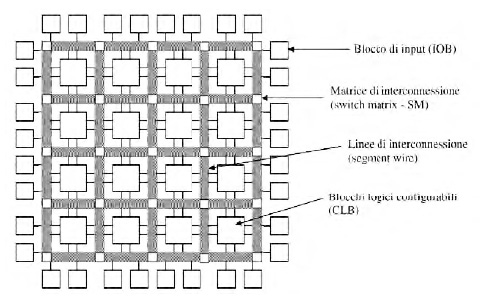

Una FPGA (al seguente link un approfondimento) è un circuito di tipo VLSI e può essere pensato come costituito da tre blocchi fondamentali (Figura 2):

- Configurable Logic Block (CLB).

- Interconnessioni:

- Linee di interconnessione (segment wire).

- Matrici di interconnessione (SM = Switch Matrix o Switch Module). - Input/Output Block (IOB).

Figura 2: una FPGA è costituita da tre blocchi funzionali: CLB (Configurable Logic Block), interconnessioni e IOB (Input/Output Block)

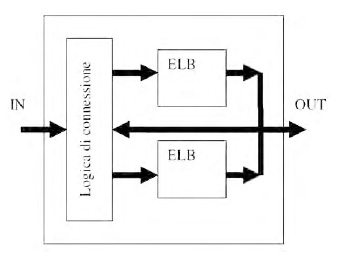

I CLB sono elementi disposti in una matrice quadrata e permettono la realizzazione di una o più funzioni logiche. Il numero di funzioni logiche implementate è determinato dal numero di circuiti logici elementari (detti EBL) presenti all’interno. Normalmente si ha anche una logica che permette la distribuzione degli ingressi verso gli ingressi degli ELB. Un ELB generalmente implementa una rete sequenziale. La struttura di un CLB è mostrata in Figura 3.

Figura 3: i CLB sono elementi disposi in una matrice quadrata e consentono di realizzare una o più funzioni logiche

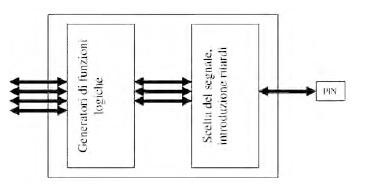

Gli Input/Output Block sono dedicati alla configurazione e alla trasformazione del segnale di ingresso/uscita. Un schema di principio è mostrato in Figura 4.

ACTEL IGLOO

Si tratta della famiglia di FPGA della Actel che meglio soddisfa, contemporaneamente, le richieste di bassi consumi e ridotta area occupata. Tali due requisiti sono fondamentali per i dispositivi portatili. Essi sono basati su tecnologia Flash ed architettura FPGA di tipo ProASIC3: con una tensione operativa di 1.2V/1.5V permettono di ridurre i consumi fino a 5 W. La famiglia dei device IGLOO supporta fino a 3 milioni di gate con 504kbit di SRAM dual-port, fino a 6 PLL on-board e 616 I/O general-pur-pose.

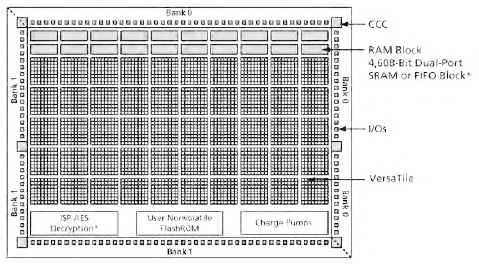

L’architettura di tali dispositivi è costituita da 6 blocchi funzionali, come illustrato in Figura 6:

- Gestione Flash*Freeze.

- VersaTiles.

- Memoria ROM dedicata.

- Memoria SRAM/FIFO dedicata.

- Circuiteria per il condizionamento del clock (PLL).

- Struttura I/O avanzata.

Figura 6: l’architettura interna di IGLOO è costituita da 6 blocchi funzionali: 1)gestione Flash*Freeze; 2) VersaTiles; 3) memoria ROM; 4) Memoria RAM; 5) Condizionamento clock; 6) Struttura I/O

TECNICHE DI LOW-POWER

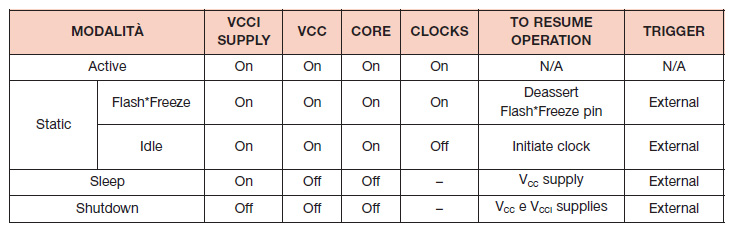

In Tabella 1 sono riportate le modalità di low-power che Actel (ora Microsemi) ha previsto per i suoi dispositivi IGLOO. Per ciascun modello sono indicate le periferiche attive e quelle disattivate durante tali modalità.

Modalità Static Idle

Nella modalità Static-Idle il clock del sistema è spento. La potenza assorbita è la minima richiesta per mantenere “in vita” il device, ossia 25 W. I pin di I/O assorbiranno solo la corrente di leakage, così come specificato dal data sheet. Durante la modalità Idle, i registri e la SRAM conserveranno il loro valore. Se si utilizza come sorgente di clock il PLL integrato, si può raggiungere la modalità idle semplicemente portando a zero il pin PLL POWERDOWN.

Modalità Flash*Freeze

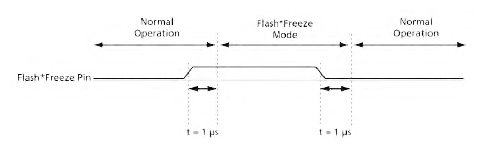

Come ulteriore sviluppo Actel (ora Microsemi) ha previsto un modalità ultra low-power che consente di ridurre il consumo, preservando il valore dei registri e lo stato della SRAM senza la necessità di spegnere il clock o l’alimentazione. Questa caratteristica, non presente negli altri tipi di FPGA, rendono IGLOO competitivo rispetto ad altri prodotti. Tale modalità prende il nome di Flash*Freeze (F*F). Esiste un apposito pin che consente di entrare ed uscire da questa modalità, che può essere pilotato dai circuiti esterni oppure dalla logica programmabile stessa (Figura 7).

Il tempo necessario per attivare o disattivare la Flash*Freeze mode è pari a 1 s, come illustrato in Figura 8, se il device risulta già alimentato.

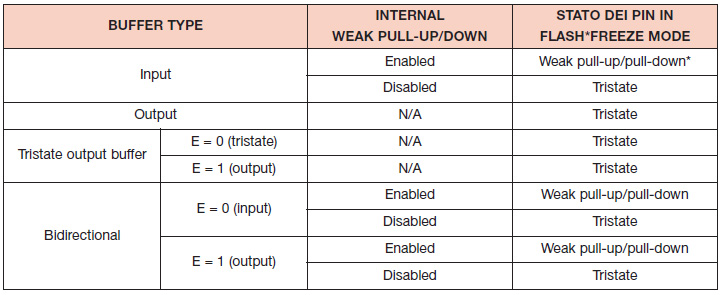

Se, invece, si accende il dispositivo già in F*F il tempo massimo richiesto sale a 5 s: questo per consentire agli I/O ed al core della FPGA di raggiungere i livelli di inizializzazione. Se si utilizza il PLL embedded, l’attivazione della modalità F*F lo spegnerà automaticamente. Al contempo, tutti i pin I/O passeranno nello stato specificato nella Tabella 2.

In particolare:

- Gli ingressi general-purpose e gli ingressi del clock alla FPGA possono continuare a funzionare senza incidere sul consumo di potenza statica.

- Le uscite sono poste in tristate.

- I pin per il JTAG restano attivi e questo permette di riprogrammare il dispositivo.

- Ovviamente, il pin F*F resta attivo, nel senso che è utilizzato per ripristinare la normale condizione operativa.

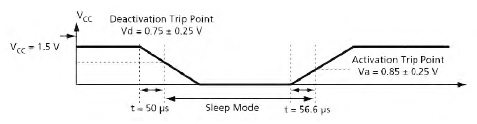

Modalità Sleep

Quando la funzionalità del dispositivo non è richiesta si può ricorrere alla modalità Sleep. In questo caso l’alimentazione (VCC) del chip è disattivata. Questo comporta un sensibile risparmio di potenza. La Tabella 3 mostra lo stato delle alimentazioni in tale modalità.

In Figura 9 si riporta il diagramma temporale per l’attivazione e disattivazione della modalità Sleep.

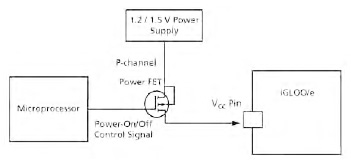

Modalità Shutdown

Serve per spegnere completamente tutte le alimentazioni del chip. La Figura 10 riporta una delle possibili soluzioni per controllare lo spegnimento e l’accensione dell’IGLOO.

Figura 10: controllo dell’accensione e dello spegnimento del dispositivo utilizzando un micro ed un FET

Actel raccomanda di utilizzare un FET con un valore di resistenza drainsource molto basso per ottenere ridotti tempi di assestamento.

A proposito di FPGA vi suggerisco questa lettura https://it.emcelettronica.com/lo-sviluppo-di-fpga-con-cortex-m1 😉