In questo articolo analizzeremo i Microcontrollori Kinetis Freescale (NXP), in particolare le tecniche di conversione analogico-digitale (ADC).

Per sviluppare il nuovo dispositivo di recupero di energia, la Mclaren Electronic System decise di iniziare una nuova partnership con Freescale Semiconductor (NXP), azienda internazionale che fornisce sistemi elettronici alla clientela. Le due parti credono che la collaborazione porterà a un miglioramento del sistema KERS della Mclaren Mercedes, e grazie all'esperienza di Freescale (NXP), tale dispositivo verrà implementato anche sulle vetture stradali. La KERS Technology Kinetis Energy Recovery System funziona come una sorta di caricatore di energia che trasmette una maggior potenza, irrigidendone la coda in uscita dalla curva. Le fibre piezoelettriche posizionate a 0° nella zona della coda trasformano l’energia meccanica in energia elettrica. Questa viene immagazzinata in un microchip e rilasciata allo sci quando è necessario. Il tempo di rilascio è controllato da uno speciale sensore. Il sensore è programmato in precedenza secondo le esigenze e gli schemi di flessione dei differenti modelli. A differenza della precedente tecnologia esclusiva di Head, la tecnologia Intelligence in campo sciistico, il KERS non influisce sulla rigidità torsionale ma controlla e modifica la flessione longitudinale e la rigidità sulla coda dello sci. Lo sci ha la massima flessione alla fine della curva, a seconda della lunghezza dello sci, del peso dello sciatore e della velocità. Nella zona dove lo sci flette di più, il sensore del microchip si attiva e rilascia l’energia alle fibre piezoelettriche. Il sistema aiuta la risposta elastica determinando un’accelerazione a fine curva. Il KERS può essere considerato come un turbo nello sci, un acceleratore che fornisce maggior potenza. Il "Turbo Booster" della sciata. Non è un dispositivo meccanico. Funziona in modo totalmente elettronico ed é visibile attraverso la superficie dello sci. Il KERS è un marchio registrato di HEAD Sport GmbH.

KINETIS FREESCALE - ADC

Kinetis è il nome della più ampia linea di microcontrollori con tecnologia ARM del settore industriale, alla data del lancio. I microcontrollori Kinetis sono basati su architettura ARM Cortex-M4, veloci e a basso consumo. La linea Kinetis usa un Thin Film Storage (TFS) di 90 nm con tecnologia Flash (FlexMemory). Inoltre, ci saranno più di 200 prodotti compatibili in periferiche e package. Il processore ARM Cortex-M0+ offre maggiore efficienza energetica, prestazioni e facilità d’uso rispetto al predecessore, Cortex-M0. Esso mantiene la completa compatibilità del set di istruzioni con tutti gli altri predecessori di classe Cortex-M-(Cortex- M0/3/4), consentendo agli sviluppatori di riutilizzare i tool di compilazione e debug già esistenti. I punti di forza di Kinetis sono una tecnologia flash memory proprietaria a 90 nm chiamata Flex Memory, che usa la ridondanza per offrire uno storage EEPROM con una durata fino a 10 milioni di cicli, 1000 volte superiore a quella delle celle esistenti e quello di avere il possesso del sistema operativo real time (RTOS) MQX, l’ambiente di sviluppo integrato Code Warrior di Freescale. Quest’ultimo permette che il codice possa essere trasferito ad ogni dispositivo Coldfire o ARM a 8-bit, 16-bit o 32-bit, con ogni combinazione di periferiche, dato che i driver di livello basso sono generati in tempo reale.

È previsto anche il lancio della IDE per Eclipse. Le MCU Kinetis series L sono realizzate sulla base del processore ARM Cortex-M0+ con un innovativo progetto della piattaforma a basso consumo, delle modalità operative e delle periferiche a risparmio energetico. La serie L di Kinetis offre una nuova combinazione di efficienza energetica, scalabilità, valore e facilità d’uso nell’area delle MCU entry-level. Essa offe a chi già utilizza architetture a 8 e 16 bit un percorso di migrazione verso le MCU Kinetis a 32 bit, consentendo di aggiungere maggiori prestazioni e funzionalità nei prodotti finiti, pur mantenendo un basso livello di consumo energetico e di costo di sistema. Ogni famiglia combina eccellenti valori delle correnti dinamiche e di stop con superiori prestazioni di elaborazione, una ricca scelta di memorie Flash e diverse opzioni analogiche, di connettività e periferiche HMI.

La famiglia KL0 è pin-compatibile con la famiglia a 8 bit S08Px e costituisce un ponte per gli sviluppatori nel portafoglio Kinetis, oltre ad essere compatibile in software con le altre famiglie Kinetis serie L. Le famiglie KL1/2/3/4 sono tutte fra loro compatibili in hardware e in software, e così pure con le loro equivalenti Kinetis serie K, basate sul Cortex-M4 (KL1->K10, KL2->K20…). Ciò consente agli sviluppatori di seguire un percorso di migrazione scalabile in avanti e indietro, allo scopo di integrare maggiori o minori prestazioni, memoria e funzioni, per poter riutilizzare l’hardware e il software sulle piattaforme del prodotto finito e ridurre il time-to-market.

CARATTERISTICHE PRINCIPALI

Le principali caratteristiche sono: 1.77 CoreMark/MHz, da 2 a 40 volte più dei dispositivi a 8/16 bit, 9% più del Cortex-M0, CoreMark/mA da 2 a 50 volte più delle MCU a 8/16 bit, il 25% più del Cortex M0 Pipeline a due stadi, meno cicli per istruzione (CPI) per consentire più veloci istruzioni di branch e ISR entry Micro Trace Buffer, soluzione di traccia leggera e non intrusiva. Informazione di traccia memorizzata in una piccola area della SRAM della MCU (di dimensione definita dal programmatore), SWD/JTAG read over, ampio supporto di ecosistema ARM, accesso di I/O in singolo ciclo, frequenza di toggling GPIO il 50% più elevata degli I/O standard per aumentare il tempo di reazione agli eventi esterni, consentendo il bit-banding e l’emulazione del protocollo software, spazio di indirizzamento lineare di 4 GB, elimina complessi schemi di paginazione semplificando l’architettura software, set di istruzioni compatibile al 100% con il processore Cortex-M0, sottoinsieme del set di istruzioni del processore Cortex- M3/4. La migliore densità di codice della sua classe rispetto alle architetture a 8/16 bit riduce la dimensione della memoria Flash (e il relativo costo) e il consumo energetico, pur superando le controparti a 8 e 16 bit. L'accesso alla memoria di programma in cicli alterni riduce il consumo energetico. Le caratteristiche comuni a tutte le famiglie di MCU della serie L di Kinetis sono:

- Massima efficienza di elaborazione

- Processore ARM Cortex-M0+ a 48 MHz

- Peripheral Bridge Crossbar

- Controllore di memoria Flash con zero

stati d’attesa - Modalità a bassissimo consumo

- Tecnologia Flash a basso leakage da 90

nm - Modalità multiple RUN, WAIT e STOP

- ADC a 12/16 bit

- DAC a 12 bit

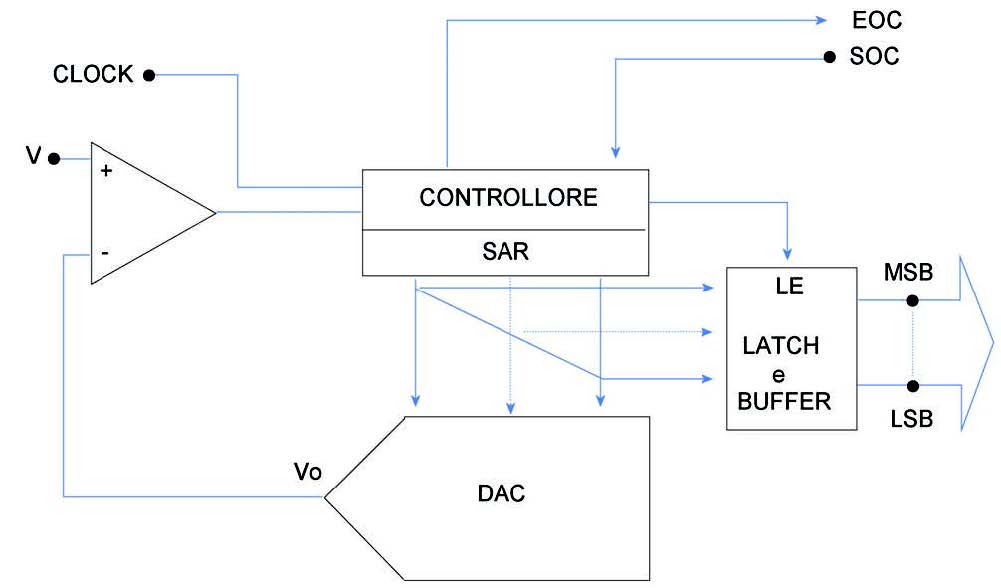

La famiglia K10 dispone di 2 convertitori analogico-digitali (tecnologia SAR) da 16 bit ad elevata velocità (tempo di conversione pari a 500 ns), con risoluzione configurabile dall’utente, e modalità di uscita singola o differenziale per una migliore immunità al rumore. La tecnologia SAR (approssimazioni successive) è tipica nelle architetture che richiedono risoluzioni medio-alte, con tempi di conversione inferiori ai 5 Msps. SAR ADC occupano solitamente una gamma di risoluzione tra gli 8 ed i 16 bit e possono essere realizzati con tecnologie a basso consumo e di piccole dimensioni. Questo li rende adeguati per l’integrazione in microcontroller embedded, in apparecchi portatili e a batteria, pen digitizers, controlli industriali, acquisizione di dati e segnali di impiego generale. Lavorano su approssimazioni successive con un registro binario. Il tempo di conversione aumenta con l’aumentare della risoluzione. Analizzando la struttura generale di un convertitore SAR (Figura 1) notiamo la presenza di due componenti critici: il comparatore e il DAC. Il circuito sample/hold è in genere inglobato nel DAC e non può essere considerato un blocco a sé stante.

Figura 1: ADC ad approssimazioni successive

La velocità di un ADC SAR è limitata dai seguenti fattori: tempo di assestamento del DAC (assestamento della tensione in uscita quando si cambia configurazione in ingresso), velocità di comparazione del comparatore di piccole differenze tra Vin e Vdac, ritardo dei circuiti digitali che implementano la logica SAR. Ecco di seguito alcuni esempi di confronto di tecnologie.

SAR vs Pipeline

Un convertitore di tipo Pipeline utilizza una struttura parallela in cui ogni stadio lavora su uno o pochi bit contemporaneamente. Questo parallelismo incrementa le spese di consumo di potenza e di latenza (latency). La latenza in questo caso è definita come il tempo che intercorre tra il momento dell'acquisizione di un campione ed il tempo in cui il dato digitale è prelevabile all’uscita del DAC. Un ADC Pipeline prende più area di silicio rispetto ad un SAR equivalente. Inoltre, Pipeline con più di 12 bit richiedono strutture di trimming o di calibrazione come per un SAR.

SAR vs Sigma Delta

Tradizionalmente, i convertitori Sigma Delta sono utilizzati in applicazioni audio con banda limitata a 22kHz. Il convertitore SD ha il vantaggio di non richiedere trimming o calibrazioni anche per risoluzioni di 16-18 bit e di non richiedere filtri di anti aliasing visto il sovra- campionamento rilegando alla parte digitale il compito del filtraggio.

Riepilogando, i vantaggi di un SAR sono:

- basso consumo;

- bassa occupazione di area;

- alta risoluzione e accuratezza.

Mentre gli svantaggi di un SAR sono:

- bassa frequenza di campionamento;

- specifica accuratezza dei blocchi.