Sul blog di Elettronica Open Source puoi leggere non solo tutti gli articoli Premium riservati agli abbonati Platinum 2.0 e inseriti nella rivista Firmware 2.0 (insieme ad articoli tecnici, progetti, approfondimenti sulle tecnologie emergenti, news, tutorial a puntate, e molto altro) ma anche gli articoli della Rubrica Firmware Reload. In questa Rubrica del blog abbiamo raccolto gli articoli tecnici della vecchia rivista cartacea Firmware, che contengono argomenti e temi evergreen per Professionisti, Makers, Hobbisti e Appassionati di elettronica. I convertitori AD rappresentano una pietra miliare dell’elettronica moderna senza la quale l’elaborazione numerica e la trasmissione digitale dei segnali non sarebbero nemmeno pensabili. In questo articolo ne discuteremo le architetture. Particolare enfasi sarà data ad una serie di considerazioni sui convertitori AD più diffusi nell’elettronica applicata: gli ADC ad approssimazioni successive (SAR).

ERRORI DEI CONVERTITORI AD

La prima inevitabile ed ineliminabile causa di errore di un ADC è legata al processo di quantizzazione. A questi vanno aggiunti l’errore di non linearità, l’errore di guadagno, l’errore di offset. Questi ultimi sono dovuti ad imperfezioni fisiche e quindi parametriche dei circuiti che implementano l’ADC. In un ADC a 8 bit, per esempio, un errore di 1 LSB significa un errore pari ad 1/256 della dinamica (0,4%) ed è anche un modo per dire che l’ultimo bit della conversione è sostanzialmente casuale. Va inoltre considerato che mentre il funzionamento in presenza di un segnale di ingresso costante si avvicina molto a quello ideale, in condizioni dinamiche può divenire abbastanza differente. Tempi di assestamento e di risposta non ideali, slew-rate dei dispositivi attivi che fanno parte dell’ADC, imprecisioni del circuito di temporizzazione, rumore, guadagno non ideale dei comparatori, instabilità di parametri elettrici quali resistenze, offset degli amplificatori, fluttuazioni della tensione di alimentazione e di quelle di riferimento, sono tutte cause che influiscono sull’errore complessivo della conversione. Per fortuna, difficilmente tutte queste cause producono errori che si sommano con lo stesso segno. Analizziamo brevemente alcuni di questi errori.

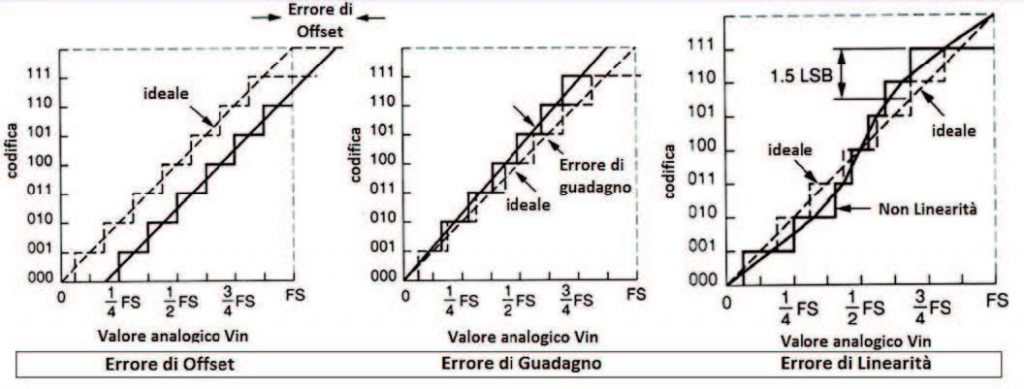

Errore di guadagno. Graficamente (Figura 1) è una variazione della pendenza della retta interpolante la gradinata rispetto a quella ideale. Generalmente è causato da una tensione di riferimento o da amplificazioni o attenuazioni che si discostano da quelle nominali teoriche di progetto. Teoricamente è possibile una correzione attraverso taratura.

Errore di offset. Graficamente (Figura 1) è una traslazione, parallelamente a se stessa, della curva caratteristica a gradinata. Ciò può comportare che l’ADC fornisca un codice di uscita diverso da zero anche per campioni di valore nullo. Opportune tarature possono consentire la correzione dell’offset. L’errore, se presente, si ripercuote, in ogni caso, allo stesso modo su tutti gli intervalli di quantizzazione.

Errore di linearità. La curva ideale di trasferimento di un ADC è data da un gradinata interpolata con una retta. L’errore di linearità è una deviazione della curva interpolante la gradinata reale (b) rispetto alla retta interpolante quella ideale (Figura 1).

Figura 1: Errore di offset, di guadagno e di linearità di un ADC visti sulla caratteristica statica di trasferimento

ADC A GRADINATA (O A CONTATORE O A RAMPA NUMERICA)

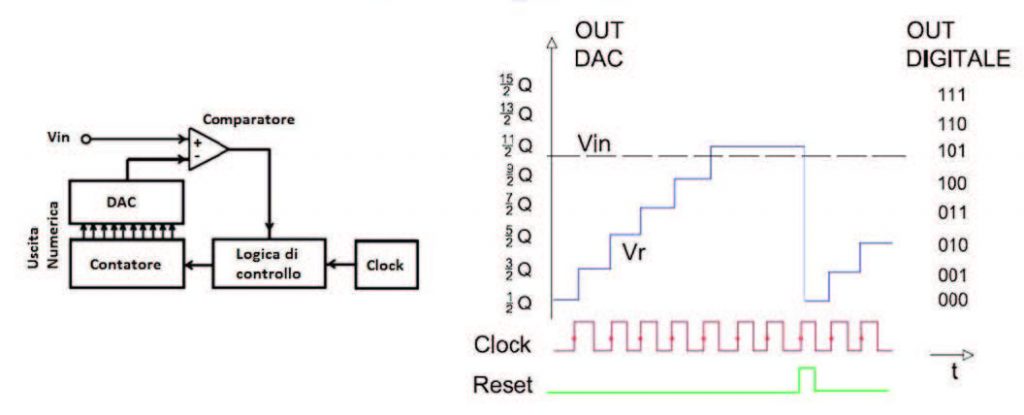

Sono formati da un DAC, un contatore in salita ed un comparatore: la conversione inizia posizionando il circuito di sample-hold in modalità HOLD. Inizialmente il contatore è nello stato 0, quindi l’uscita del comparatore è alta (Vin>0) per cui la logica di controllo consente l’incremento del contatore. A ogni ciclo di clock si ha un incremento finché la tensione sull’ingresso invertente non supera Vin (Figura 2). A questo punto, il contatore interrompe il conteggio ed il suo contenuto è la codifica del campione. Il tempo di conversione risulta variabile e dipendente da Vin. Poiché il numero massimo di passi per la conversione è 2n (che si ha per Vin=VFS ), la massima frequenza di campionamento possibile è pari alla frequenza del clock divisa per 2n.

Figura 2: Architettura di un ADC a rampa numerica ed esempio di evoluzione del contatore interno

CONVERTITORE AD INSEGUIMENTO O TRACKING (O SERVOCONVERTITORE)

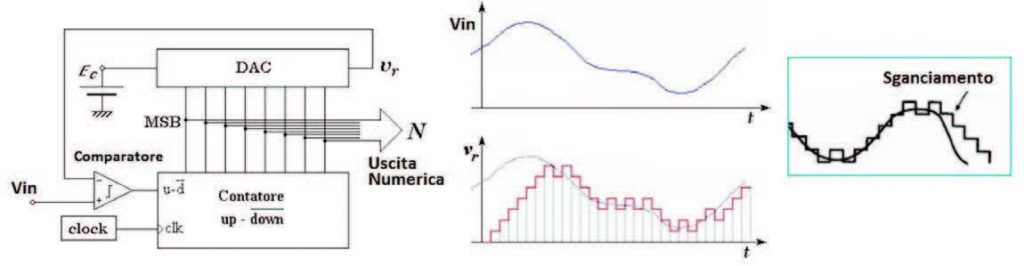

Una variante dell’ADC a rampa numerica è il convertitore a inseguimento (tracking) che si ottiene sostituendo il contatore in salita con un contatore up/down. Supponendo che inizialmente il registro di uscita del contatore sia nello stato N=0, la tensione di uscita del DAC è nulla. Il contatore “up-down” incrementa il contenuto del registro di uscita se, in corrispondenza dei fronti di clock, l’ingresso di controllo u-d presenta il livello logico H; in caso contrario ne determina il decremento. Da questo semplice algoritmo deriva l’effetto di inseguimento. Il transitorio iniziale consente di agganciare il segnale Vin; da questo momento in poi l’uscita numerica N si mantiene in prossimità del valore istantaneo di Vin incrementando il suo valore se Vin aumenta, decrementandolo se Vin diminuisce. Se il segnale d’ingresso non ha variazioni troppo rapide, il tempo di aggancio risulta contenuto e l’uscita binaria continua a seguire l’ingresso senza necessitare di segnali di reset o di fine conversione. Il tempo di conversione può risultare lungo in occasione della conversione del primo campione; successivamente tutto è più rapido poiché il contatore non riparte da 0, ma dal valore in cui si trovava precedentemente. Un piccolo inconveniente si ha nel fatto che si genera un’oscillazione, anche se Vx è costante. Ovviamente, il convertitore aggancia il segnale e rimane agganciato se il segnale analogico in ingresso presenta una velocità di variazione contenuta. Possiamo affermare semplicemente che la massima velocità di variazione di Vin (espressa in V/s) tollerata deve risultare inferiore di 1LSB/Tc dove Tc è il periodo di campionamento. In Figura 3 è mostrato il processo di aggancio. Se il contatore viene fatto partire da VFS/2 il tempo di aggancio è inoltre più contenuto. Se invece il segnale varia troppo rapidamente, ammesso che si verifichi l’aggancio, può successivamente verificarsi anche il fenomeno dello sganciamento (Figura 3).

Figura 3: Architettura dell’ADC ad inseguimento, aggancio e sgancio del segnale

CONVERTITORI A SINGOLA E DOPPIA RAMPA (O AD INTEGRAZIONE)

Sono ADC basati sulla conversione tensione-tempo. Sfruttando la carica di un condensatore ed il conteggio, attraverso un contatore, del tempo necessario perché la carica raggiunga una certa tensione di riferimento. Così facendo, si effettua di fatto una conversione tensione-tempo ed in pratica la conversione A/D. Il pregio sta principalmente nel poter ottenere una risoluzione arbitrariamente alta incrementando il tempo di carica del condensatore senza complicare l’architettura circuitale. Gli errori sono quelli tipici di altri convertitori. Non vi è però dipendenza da alcun DAC mentre vi è dipendenza dalla deriva nel tempo e con la temperatura del prodotto RC. La tecnica si adotta quando sono richieste precisioni elevate e sono tollerate velocità di conversione molto basse. La semplicità costruttiva e l’attenuazione dei disturbi dovuta proprio alla conversione per integrazione sono i pregi più significativi.

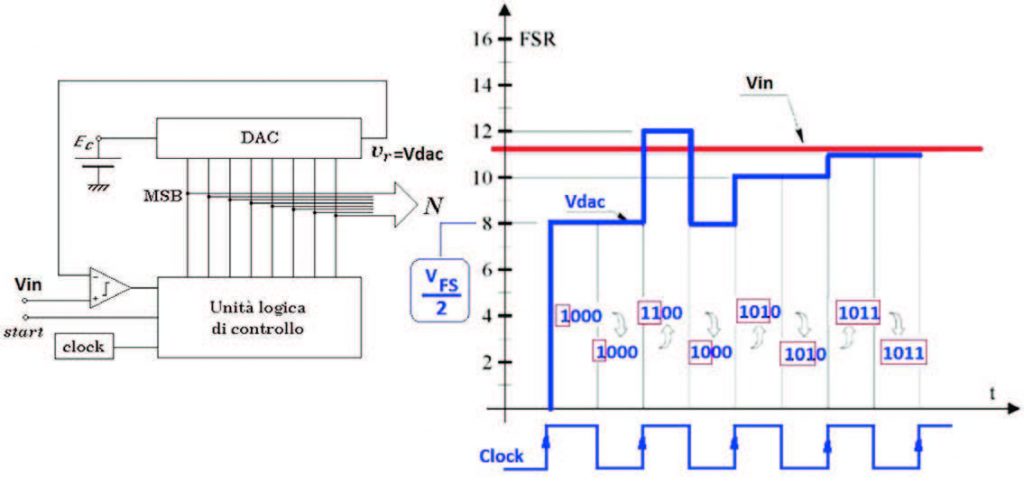

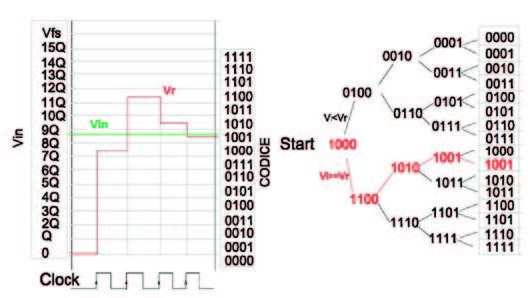

CONVERTITORE AD APPROSSIMAZIONI SUCCESSIVE (AD SAR-SUCCESSIVE APPROXIMATION REGISTER)

L’architettura di un AD-SAR prevede l’impiego di un circuito sample-hold, un comparatore, un DAC (Convertitore Digitale Analogico), un registro ad approssimazioni successive (SAR appunto) e una temporizzazione. L’architettura è in effetti simile a quella del convertitore a gradinata, salvo la sostituzione del contatore con un Successive Approximation Register. La conversione avviene sempre in n passi (Figura 4).

Figura 4: Architettura dell’ADC ad approssimazioni successive (AD: SAR) e relativa procedura di conversione

Il SAR pone ad 1 il bit più significativo (MSB-Most Significant Bit), che corrisponde a metà valore di fondo scala. Il comparatore confronta l’uscita del D/A con il valore del campione ed in base all’esito di questo confronto decide se lasciare questo bit ad 1 (uscita D/A < ingresso) o se porlo a 0 (uscita D/A > ingresso). Le limitazioni dal punto di vista dell’accuratezza della conversione derivano dal rumore dell’amplificatore d’ingresso e del comparatore, dalla stabilità del riferimento di tensione e dall’errore del DAC. La tecnica consente elevate risoluzioni, orientativamente da 8 a 18 bit, basso consumo (versioni CMOS) e velocità di conversione intermedie (generalmente inferiori ad 1 MSPS). Occorre infatti un ciclo di clock per ogni bit e quindi complessivamente n cicli di clock per completare la conversione, indipendentemente dal valore del campione. L’oscillatore locale (clock) che cadenza le fasi di conversione non è causa di errore e può quindi essere costituito anche da un semplice oscillatore RC. Il campione sottoposto a codifica è compreso tra 11 ed 11,5 per esempio Vin=11,23. Analizziamo più in dettaglio i passi del processo.

Passo 1 (primo colpo di clock)

Si imposta ad 1 il primo bit più significativo. Prima approssimazione: 1000. Il codice corrispondente secondo il DAC a Vr=8. Poiché Vin=11,23>8 il bit viene lasciato definitivamente ad 1.

Passo 2 (secondo colpo di clock)

Si imposta ad 1 il secondo bit più significativo. Seconda approssimazione: 1100. Il codice corrispondente secondo il DAC a Vr=12. Poiché Vin=11,23<12 il bit viene modificato e fissato definitivamente a 0.

Passo 3 (terzo colpo di clock)

Si imposta ad 1 il terzo bit più significativo. Terza approssimazione: 1010. Il codice corrispondente secondo il DAC a Vrif=10. Poiché Vin=11,23>10 il bit viene lasciato definitivamente ad 1.

Passo 4 (quanto colpo di clock)

Si imposta ad 1 il quarto bit più significativo. Quarta approssimazione: 1011. Il codice corrispondente secondo il DAC a Vrif=11. Poiché Vin=11,23>11 il bit viene lasciato definitivamente ad 1. E’ stato raggiunto il quarto colpo di clock=num. di bit di codifica. Il processo ha termine e CODICE=1011.

In pratica, la dinamica della conversione evolve fino a quando i due ingressi del comparatore differiscono di una quantità inferiore alla risoluzione del convertitore, cosa che fa cambiare lo stato logico dell’uscita dello stesso comparatore. Giunti a questo punto il codice in uscita al SAR costituisce la codifica del campione in oggetto. L’algoritmo risale a Tartaglia (XVI sec.) come soluzione al problema di determinare il peso di un oggetto equilibrando una bilancia a due piatti utilizzando il minor numero possibile di pesi standard. Il convertitore opera una conversione via via più fine partendo dal bit più significativo (MSB) fino a giungere a quello meno significativo (LSB). Visto da un’altra prospettiva, possiamo dire equivalentemente che l’ADC SAR funziona secondo la logica della ricerca dicotomica. L’esempio di Figura 5 ne mostra in maniera evidente il perché. Esso si riferisce ad una codifica binaria pura a 5 bit.

Figura 5: Conversione ADC SAR a 4 bit vista come processo di ricerca dicotomica

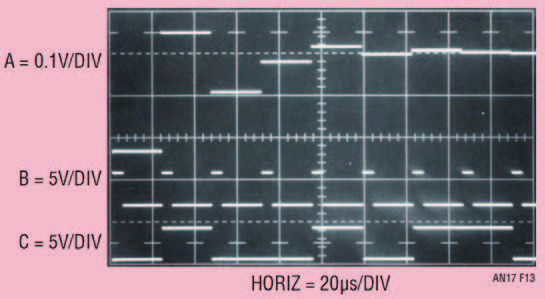

Ovviamente, si sono proposti esempi con 4 o 5 bit di conversione per motivi di opportunità ma senza ledere in alcun modo la generalità di quanto esposto. E’ evidente il vantaggio in termini di velocità di conversione di un ADC ad approssimazioni successive rispetto ad un ADC a gradinata. All’incertezza di quantizzazione, intrinseca nel processo, si sommano effetti dovuti all’instabilità di Ec, alla non linearità del DAC, al guadagno non infinito ed all’offset del comparatore. L’ADC-SAR conserva in ogni caso il pregio di consentire un ottimo compromesso tra risoluzione (sufficientemente elevata, fino a 18 bit), rapidità di conversione ed economicità da cui la sua maggiore diffusione rispetto ai suoi concorrenti. L’algoritmo di conversione rimane semplice: all’inizio della conversione il SAR contiene il codice binario corrispondente alla metà del valore di fondo scala (per esempio 1000 in un ipotetico convertitore a 4 bit). All’inizio di ogni passo di conversione, il relativo bit del SAR viene impostato provvisoriamente a 1 e viene generata dal DAC la tensione analogica VR corrispondente al codice presente nel SAR. Se il campione da convertire è maggiore di Vr l’uscita del comparatore è alta ed il bit del codice in questione rimane 1, in caso contrario l’uscita del comparatore è bassa ed il bit viene modificato in 0. Appare evidente come la velocità, la precisione e la linearità di un ADC SAR dipendano principalmente dalle caratteristiche del DAC e del comparatore. I primi moduli convertitori SAR prodotti da Analog Devices risalgono al 1969. Con l’avanzare della tecnologia tutte le case di semiconduttori hanno prodotto modelli di ADC-SAR sempre più veloci e con risoluzioni sempre maggiori fino a 14, 16 e 18 bit con ingresso unipolare o bipolare, single-ended o differenziale, con uscita parallela o seriale, integrazioni sempre più spinte e consumi di potenza e costi sempre più ridotti, migliorando linearità e rapporto segnale-rumore. L’impiego di tecnologie CMOS sempre più submicrometriche ha favorito questo processo ed ha consentito agli ADC-SAR di raggiungere velocità di conversioni anche di dieci MSPS. La Figura 6 mostra il comportamento descritto fino a questo momento per un ADC-SAR ad 8 bit rilevato attraverso un oscilloscopio.

Figura 6: Analisi all’oscilloscopio dell’evoluzione temporale di una conversione ADC-SAR. La convergenza aumenta ad ogni step (Traccia A) cioè ad ogni colpo di clock (traccia B) pilotata dall’uscita del comparatore (traccia C)

L’errore ad ogni step (traccia A), il clock (traccia B) ed il risultato della comparazione che determina l’evoluzione stessa del registro SAR (traccia C) seguono esattamente il tipo di comportamento fin qui discusso. L’errore converge via via fino a ridursi al più ad ½ LSB esattamente come si ottiene con il bilanciamento dei pesi in una bilancia a due piatti.