Le caratteristiche fondamentali di un sistema costruito intorno ad un microcontrollore PSoC, che utilizza il protocollo DMX per la gestione remota della luminosità e della potenza fornita agli impianti di illuminazione.

Introduzione

Il Dimmer è un regolatore elettronico utilizzato per limitare la potenza inviata ad un carico: esso può basarsi su un reostato per la regolazione della tensione oppure può variare il duty-cycle di alimentazione dell’utilizzatore mediante modulazione della larghezza di impulso. Esistono in commercio circuiti integrati progettati esclusivamente per svolgere tale compito; le funzioni loro affidate possono essere molto complesse, basti pensare ai dispositivi che regolano l’intensità luminosa di interi apparati come quelli presenti nei teatri o nelle sale da concerto. In molte applicazioni tale controllo avviene a distanza, per cui è necessario affidarsi ad un protocollo di comunicazione che trasferisca i dati, relativi alla potenza e alla luminosità volute, ad un numero anche elevato di canali di utilizzo; in tal caso il dimmer tradurrà il segnale in input, veicolato dal protocollo, in un valore di tensione da applicare al carico. Nel paragrafo successivo si vedranno brevemente le caratteristiche del protocollo di comunicazione DMX (Digital Multiplex).

PROTOCOLLO DMX

Il protocollo DMX è stato stabilito nel 1986 dall’USITT (United States Institute for Theatre Technology) ed è diventato da allora l’interfaccia standard di comunicazione tra dispositivi destinati all’illuminazione. Esso si affida allo standard RS485, che definisce i valori di tensione e di corrente dei segnali che costituiscono il data-stream. Questo standard prevede che le “masse” dell’apparato trasmittente e ricevente siano collegate al conduttore che fa da schermo nel cavo di trasmissione, in modo da diminuire l’influenza di rumore esterno e di migliorare la sicurezza elettrica; per evitare la formazione di anelli di massa e il conseguente flusso di corrente entro lo schermo, è necessario isolare elettricamente i ricevitori DMX (per esempio tramite foto-accoppiatori). La figura 1 riporta la struttura tipica del flusso dei segnali dello standard DMX512; i vari pacchetti iniziano con un segnale di sincronismo della durata minima di 88 microsecondi (indicato con 1 nello schema), cui fa seguito uno Start byte; questo informa il dispositivo ricevente che inizia la trasmissione vera e propria dei dati, codificati nei byte relativi ai vari canali; il numero di questi varia, in questa versione del protocollo, da un minimo di 24 fino a 512: ogni canale trasporta l’informazione relativa alla luminosità voluta e per ciascuno di essi sono previsti 256 valori diversi, che si tradurranno in altrettanti livelli di potenza nell’utilizzatore associato.

Se si utilizza il massimo numero di canali a disposizione la frequenza di aggiornamento dei dati scende a 44 Hz (più che sufficiente nella gran parte delle applicazioni), altrimenti, con soli 24 canali, la frequenza è di 836 Hz (il bit-rate del DMX è di 250Kb al secondo). Un segnale con una durata maggiore di un secondo può porre il dispositivo controllato in sleep-mode. Un DMX Dimmer tipico prevede dunque una Cpu, in grado di interpretare il data-stream in input (che codifica l’intensità luminosa relativa a tutti i canali di utilizzo) e di tradurlo successivamente in segnali adatti a pilotare il circuito di potenza; nel prossimo paragrafo si esamina l’anello finale della catena di controllo, ovvero un possibile circuito di alimentazione basato su TRIACs.

CIRCUITO DI POTENZA CON CONTROLLO DI FASE

Un circuito di collegamento tra driver di potenza (TRIAC) e utilizzatore è mostrato nella figura 2.

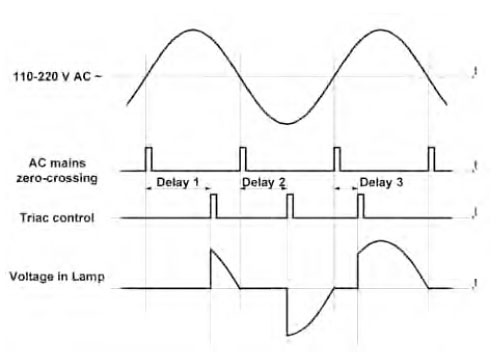

La configurazione adottata permette di variare la luminosità della lampada controllando il ritardo temporale esistente tra il “zero-crossing” della tensione di rete e l’istante in cui il Triac viene posto in conduzione: il controllo avviene tramite un segnale proveniente dalla Cpu. Esaminiamo infatti i diagrammi riportati in figura 3: quando un impulso di controllo (positivo o negativo) è inviato al gate del Triac, questo si pone in conduzione e la tensione AC alimenterà la lampada con una forma d’onda variabile in funzione dei vari ritardi applicati.

Il passaggio dallo stato di conduzione a quello di interdizione (spegnimento) avverrà automaticamente quando la sinusoide della tensione AC ripasserà nuovamente per lo zero (ciò avviene per le caratteristiche intrinseche dei Triacs). Il principio di funzionamento dovrebbe a questo punto risultare chiaro: quanto più i delays applicati sono brevi, maggiore sarà la potenza fonita alla lampada. L’occhio provvederà poi ad “integrare” le varie forme d’onda ricavate, “traducendole” in un particolare valore di luminosità; ogni data-byte del flusso DMX consisterà dunque in una codifica dei valori dei vari delays da applicare ai relativi canali. Va notato il fatto che il controllo di fase deve tener conto della frequenza della tensione AC. Se questa cambia andranno modificati opportunamente i valori dei ritardi per il corretto funzionamento del dispositivo. È dunque necessario effettuare un’operazione di calibrazione preventiva che fornisca una misura accurata della frequenza di rete: i dettagli di questa operazione saranno analizzati in seguito.

DMX DIMMER: PRINCIPIO DI FUNZIONAMENTO

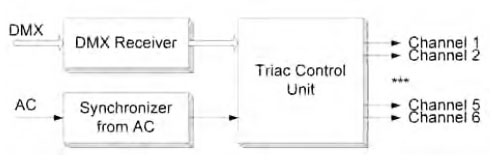

Lo schema riportato nella figura 4 illustra i blocchi rappresentativi dell’intero sistema: il ricevitore posto sul bus DMX analizza i pacchetti in ingresso e, se questi sono accompagnati dall’indirizzo corretto, li trasferisce all’Unità di Controllo del Triac (il micro PSoC). Questo provvede poi a pilotare i sei canali (driver) secondo le modalità codificate nel pacchetto elaborato.

Il blocco generatore dei sincronismi crea un impulso di lockout ogni volta che la tensione di rete passa per lo zero: questo segnale attiva sei contatori (opportunamente inizializzati) presenti all’interno della Cpu; ciascuno di essi si fermerà poi al raggiungimento di un valore opportuno, stabilito in modo da creare il ritardo voluto tra il zero-crossing della tensione di rete e l’impulso di attivazione del Triac (vedi ancora la figura 3). In questo modo l’utilizzatore sarà alimentato con una forma d’onda corrispondente al grado di luminosità voluto. Va notato che l’alimentazione della lampada e del generatore di sincronismi deve essere la stessa per il corretto funzionamento del dispositivo. Lo schema di figura 5 rappresenta l’implementazione fisica dei blocchi concettuali esaminati in precedenza.

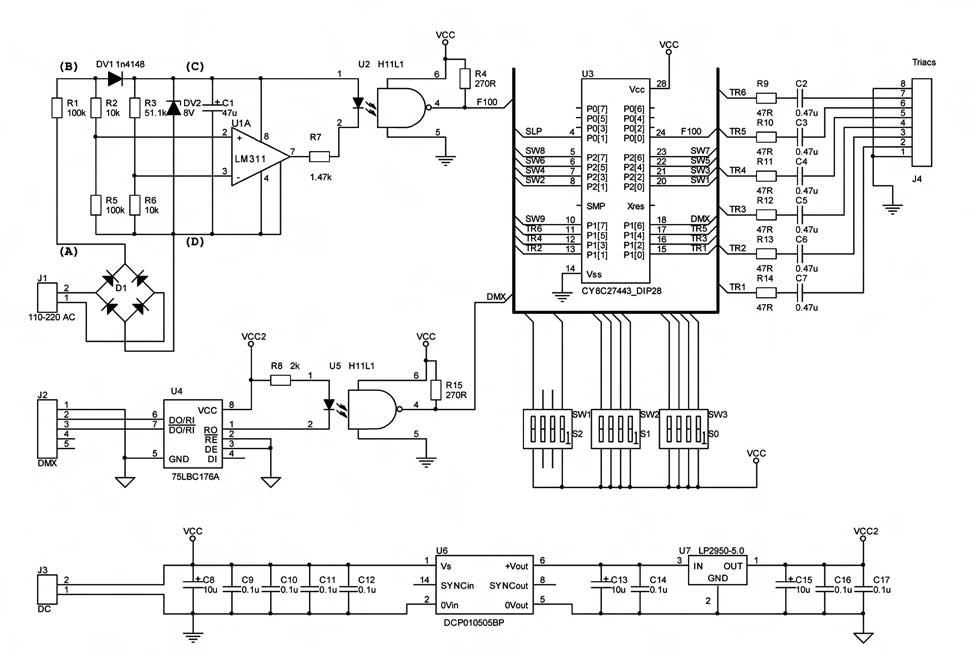

Il generatore di sincronismi è costruito intorno all’operazionale LM311, reazionato in modo da funzionare da comparatore. Le tensioni presenti in vari punti del circuito, riportate in figura 6, aiutano a comprenderne il funzionamento: il “trucco” sta nel tenere il pin 3 (ingresso invertente dell’operazionale) ad una tensione bassa (1,3volts) e il più possibile costante (il partitore R3-R6, lo zener DV2 e il condensatore C1 sono utilizzati per questo scopo), mentre sul pin 2 (ingresso non invertente) è presente una tensione variabile in un intervallo tra 8,7 e 0 volts, con la forma di sinusoide rettificata.

Nel breve intervallo di tempo in cui questa tensione oscillante si porta sotto il valore di riferimento di 1,3 volts (ovvero quando la tensione AC di rete passa per lo zero) l’uscita del comparatore commuta e l’impulso di lockout viene generato da U2, un fotoaccoppiatore che isola elettricamente lo stadio di alta tensione dal micro. L’integrato U4, specializzato per la gestione di segnali RS485, provvede a trasferire lo stream DMX a due risorse integrate nel PSoC: l’RX8, un ricevitore seriale che gestisce il flusso di dati in input, e il Counter8, utilizzato per riconoscere il segnale di break (inizio di un nuovo pacchetto). L’unità di controllo dei Triacs è fisicamente realizzata da 6 generatori PWMs secondo questo principio: il periodo del segnale PWM deve essere pari al semiperiodo della sinusoide di alimentazione di rete (vedi la procedura di calibrazione descritta in seguito), mentre il duty-cycle è pari al valore del delay che si vuole imporre tra l’AC zero-crossing e l’istante di attivazione dei triacs. I selettori indicati nella figura 5 con S1, S2 ed S3, permettono di impostare l’indirizzo del dispositivo (a 9 bits) e di attivare o meno il bus-sleep-mode: se quest’ultimo è attivo, una mancanza di segnale superiore al secondo sul bus DMX pone il dispositivo in stand-by e spegne tutti i triacs.

ANALISI DEL FIRMWARE

I pacchetti vengono ricevuti ed elaborati in tempo reale dalla sezione ricevente (l’RX8) e da alcune risorse presenti all’interno dell’unità di controllo dei triacs (il counter8, i generatori WPMs e il comparatore CMP). Per questo motivo è molto importante che il firmware separi bene queste funzioni e non faccia intervenire conflitti tra di esse. Una possibile soluzione è quella di far lavorare il microcontrollore sotto interrupts: dopo la procedura di inizializzazione e di settaggio dei vari moduli hardware, il micro diventa inattivo sino a quando non interviene una specifica richiesta da parte di una tra cinque possibili sorgenti di interrupts: a questo punto viene processata la routine associata (scritta in Assembler per minimizzare i tempi di esecuzione che sono dell’ordine dei microsecondi), e al termine la Cpu ritorna al ciclo IDLE in attesa di una nuova chiamata (i dettagli delle varie routines saranno analizzati in seguito). Nel prossimo paragrafo si vedrà la procedura di inizializzazione e di calibrazione.

Procedura di calibrazione

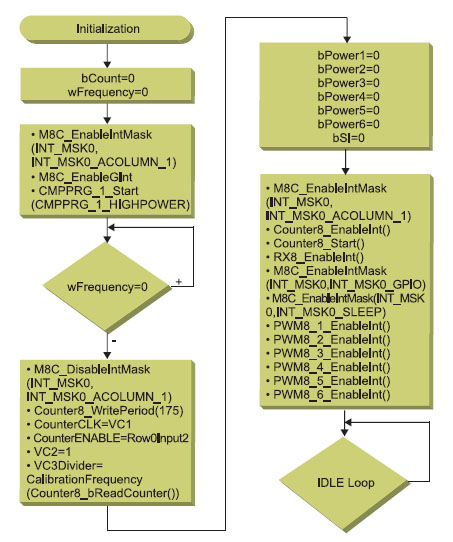

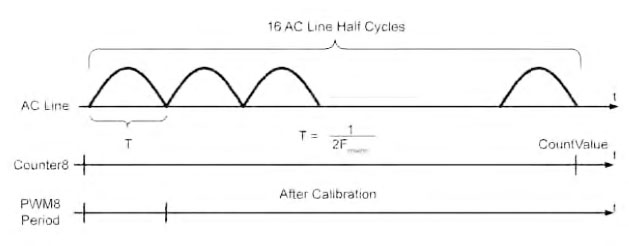

Come ricordato in precedenza, il controllo di fase presuppone la conoscenza accurata del periodo della sinusoide di alimentazione; le operazioni svolte dal Dimmer dipendono in modo essenziale dalla frequenza di rete, poiché, se si applicano gli stessi delays a dispositivi che funzionano a frequenze AC diverse, non si ottengono valori di luminosità uguali. Ecco perché la fase di inizializzazione del PSoC prevede, oltre al settaggio di variabili e dei moduli interni al micro, anche una procedura di calibrazione per la misura del periodo dell’onda AC. Vediamone in sintesi i punti salienti. All’accensione del Dimmer la procedura di calibrazione CalibrationFrequency() utilizza il contatore bCount (settato inizialmente a zero) per misurare 16 interrupts provenienti dalla prima colonna dell’Analog Block-Array integrato nel PSoC. Tali interrupts provengono da un comparatore (CMP) utilizzato per segnalare 16 zero-crossing della sinusoide di alimentazione. Quest’intervallo di tempo viene misurato da un contatore, il Counter8 (lo stesso poi riutilizzato come rivelatore del segnale di break) (vedi figura 7).

Lo scopo di questa procedura è quella di trovare il valore corretto da attribuire ad un divisore di frequenza, il prescaler VC3, che controlla direttamente il clock del segnale PWM: 256 impulsi di questo clock devono corrispondere esattamente ad un semiperiodo dell’alimentazione. In questo modo i delays da applicare per ottenere la luminosità desiderata (vedi nuovamente la figura 3) si possono rappresentare nel modo corretto tramite un certo numero (inferiore a 256) di impulsi del clock così calibrato. La figura 8 riporta le formule che traducono quanto detto.

Una volta terminata questa routine di calibrazione il flag wFrequency viene settato a 1 e si possono caricare i divisori e le variabili con i valori corretti. Il Counter8 modifica la sua funzione e viene utilizzato per segnalare l’inizio di ogni nuovo pacchetto.

DESCRIZIONE DELLE ROUTINES DI INTERRUPTUS

Il programma principale può essere realizzato in C in quanto non prevede tempi critici di esecuzione, mentre le varie routine di interrupt è bene siano scritte in assembler per rendere più veloci le relative operazioni. La funzione main() del firmware consiste di due blocchi concettuali distinti: il primo è la già citata routine di calibrazione, che va svolta all’accensione del dispositivo, l’altro riguarda l’abilitazione degli interrupts dalle varie sorgenti, l’inizializzazione del Counter8, del modulo CMP, dei generatori del segnale WPMs e il settaggio a zero delle variabili (bpower1…6) che definiscono la luminosità voluta. Dopo questa fase preliminare il micro si pone in attesa delle “chiamate” da parte delle varie periferiche che possono gestire interrupts.

- Interrupt del timer8: quando attraverso il ricevitore DMX transita un segnale di break (della durata di 44 microsecondi), viene attivata la routine di servizio del Timer8, il quale segnala l’arrivo di un nuovo pacchetto di dati e resetta il modulo RX8, destinato all’analisi del bit-stream.

- GPIO interrupt (o input interrupt): provvede a resettare il timer8 in caso di overflow, il che avviene in mancanza di un segnale di enable sulla linea DMX (mancata cattura o assenza di pacchetti).

- SleepTimerInterrupt: se è attivo lo sleep-mode, l’assenza di segnali prolungata oltre il secondo pone il Dimmer in stand-by; in tal caso le variabili di luminosità (bpower1…bpower6) vengono azzerate, a patto che il bus DMX disponga della modalità switched ON (ovvero che il dispositivo possa riaccendersi con un segnale proveniente dal bus stesso) e il flag bSI (controllato dalla routine relativa all’interrupt dell’RX8) sia uguale a zero (bus DMX inattivo).

- AnalogColumn1 interrupt: questa è una delle routine più complesse ed è attivata dal bus relativo al comparatore CMP; essa consiste di due parti: la prima è relativa alla procedura di calibrazione per la misura della frequenza di rete secondo i dettagli gia visti; l’altra provvede a fermare i generatori WPMs, a caricare le variabili di luminosità nei registri del duty-cycle e a far nuovamente partire i generatori. Va notato che durante la procedura di calibrazione si esce e si rientra nella routine di interrupt per sedici volte, tante quante sono le richieste provenienti dal comparatore che rivela il zero-crossing dell’AC (ad ogni nuova routine la variabile bCount viene incrementata di uno fino al valore sedici).

- RX8 Interrupt: la routine viene attivata quando nuovi dati provengono dal bus DMX.

CONCLUSIONI

La struttura ottimale per un dimmer multicanale può essere implementata con un sistema di due microcontrollori della famiglia PSoC: il ricevitore del flusso di dati DMX si può realizzare con un dispositivo a basso costo della famiglia CY8C21xxx, mentre per il generatore dei segnali PWMs si può ricorrere a un micro della serie CY8C29xx o ad una soluzione software usandone uno ancora della famiglia CY8C21xxx.