In applicazioni basate su parti rotanti è spesso richiesta la conoscenza della velocità angolare e della direzione di rotazione. Tali informazioni sono prelevate da un dispositivo detto encoder incrementale, che dotato di diodi laser e fotorilevatori, fornisce in uscita particolari segnali.

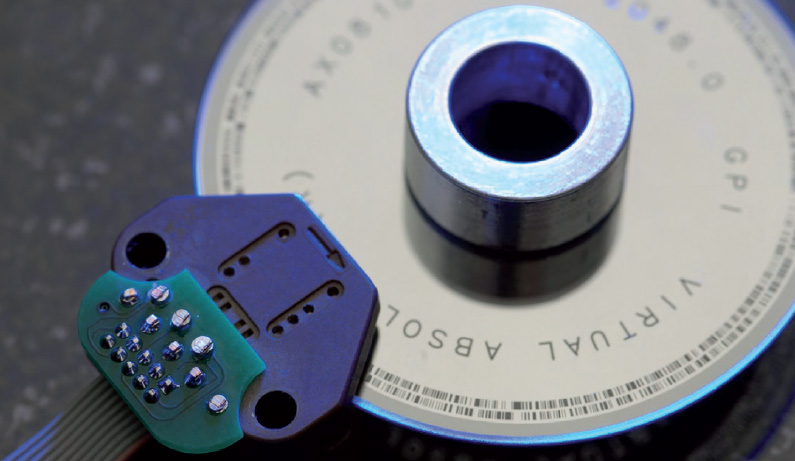

Gli encoder incrementali, detti anche ottici o quadrature encoder, sono molto utilizzati in applicazioni in cui è richiesta la misura della posizione angolare e/o della velocità di un elemento rotante. Essi forniscono in uscita un treno continuo di onde quadre, durante tutto il tempo di rotazione. A differenza degli encoder assoluti, in cui la posizione del rotore è nota a priori, negli encoder incrementali (figura 1) i segnali di uscita non forniscono di per se nessuna informazione sulla posizione angolare in un dato istante.

Figura 1: immagine di un encoder incrementale.

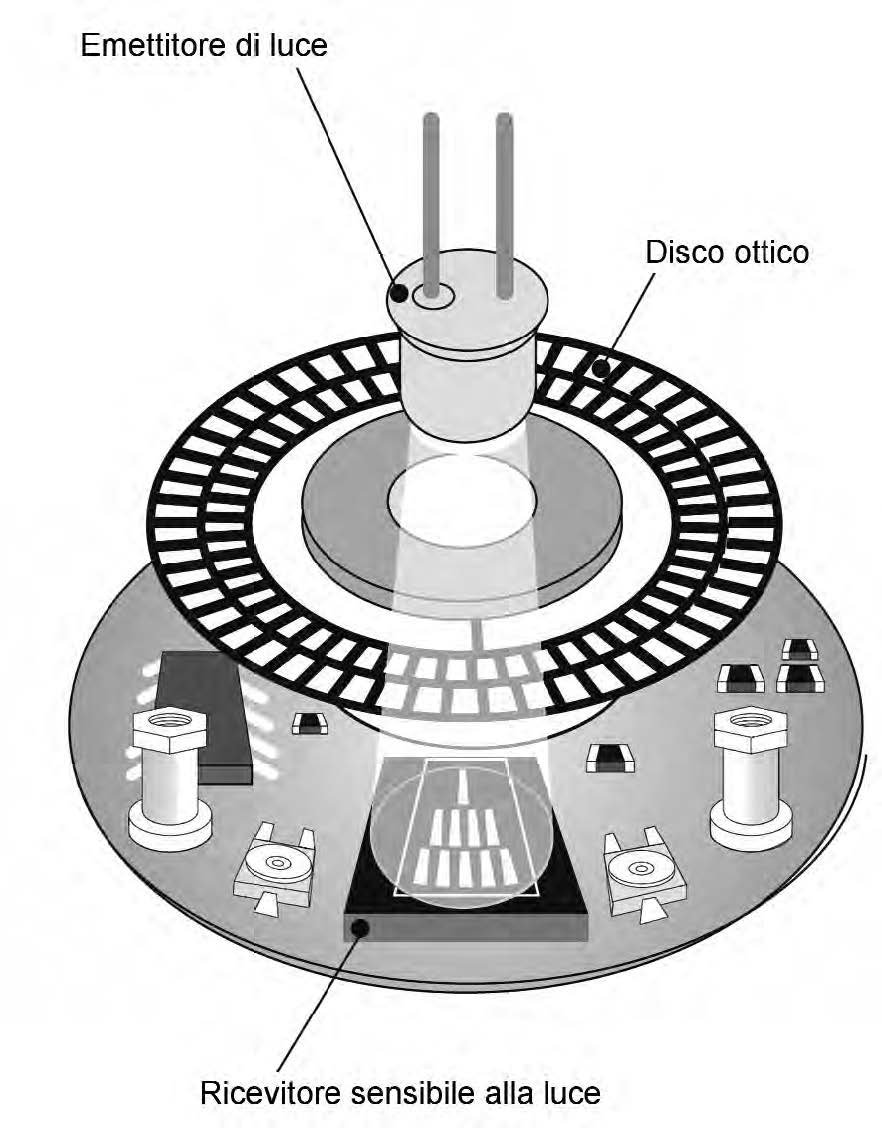

Sono molto utilizzati, poiché permettono di misurare elevate velocità angolari (fino a 9000 giri/minuto) e con un’elevatissima risoluzione (0.0001°). In figura 2 è possibile osservare lo schema costruttivo di tale encoder.

Figura 2: schema costruttivo di un encoder incrementale.

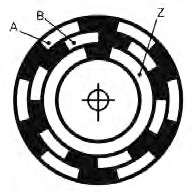

Innanzitutto, si nota la presenza di un disco interferente, costituito da due ordini di finestre trasparenti, disallineate in modo da fornire un segnale in quadratura di fase; a queste si aggiunge un terzo ordine, con una sola apertura. La figura 3 riassume perfettamente la conformazione di questo disco.

Figura 3: schema del disco interferente, presente in un quadrature encoder.

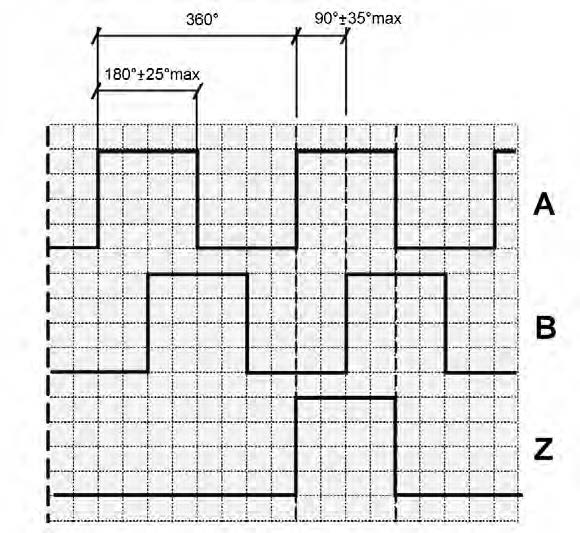

Oltre a tale disco interferente, un encoder ottico è realizzato tramite sorgenti luminose (generalmente LED, ma anche diodi laser se si vogliono ottenere risoluzioni maggiori) da una parte del disco e da fotodiodi dall’altra. La presenza di tre corone circolari che costituisco il disco interferente, permette la generazione di tre segnali differenti tra loro in sfasamento o in periodo. In figura 4 si può osservare, in termini grafici, l’andamento dei tre segnali, indicati con A, B e Z.

Figura 4: andamento dei segnali A, B, Z.

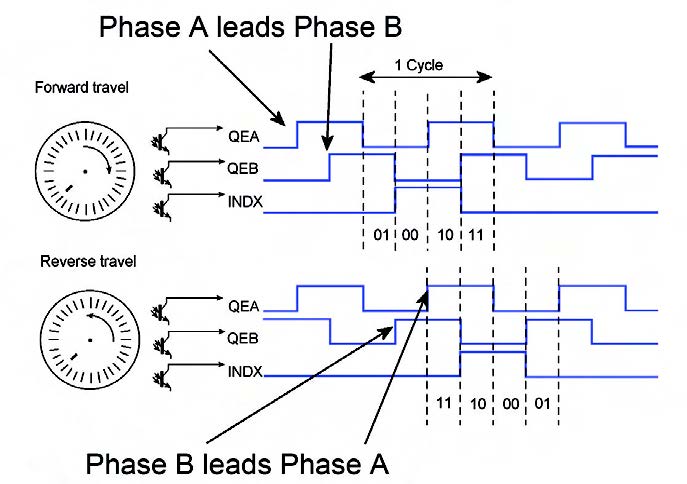

I primi due segnali sono sempre sfasati di un angolo di ±90°, per come sono costituite le due finestre più esterne del disco. In figura 5 è esplicitato tale concetto, riportando i segnali in uscita al QEI sia in caso di rotazione oraria che antioraria.

Figura 5: determinazione del verso di rotazione tramite i segnali A e B

Il segno dello sfasamento determina il verso di rotazione (orario o antiorario). Ovviamente, la velocità di rotazione è inversamente proporzionale al periodo di A e B. Invece, il segnale Z presenta un unico impulso in corrispondenza dell’unica finestra della terza corona circolare. Esso indica che il rotore ha effettuato un giro completo e serve per individuare una posizione assoluta.

Caratteristiche generali

Per l’interpretazione di questi segnali molti microprocessori dispongono di una propria interfaccia per decodificarli e fornire in automatico la velocità e verso di rotazione. In questo articolo si parlerà di un particolare modulo che caratterizza i dsPIC di Microchip: il QEI (Quadrature Encoder Interface). Per comprendere a fondo il suo funzionamento è necessario partire dal suo schema funzionale, riportato in figura 6.

Figura 6: schema funzionale del modulo QEI integrato nei dsPIC per la decodifica dei segnali provenienti da un encoder incrementale.

Filtri di rumore digitali programmabili

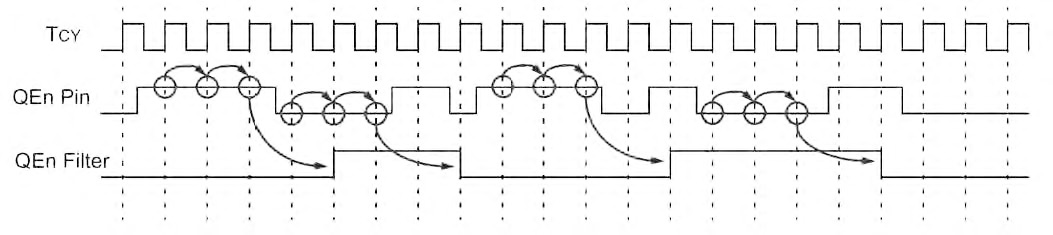

Poiché i segnali acquisiti dall’encoder sono spesso affetti da rumore, sono disponibili dei filtri digitali (blocco Digital Filter Logic in figura 7) su ciascun degli ingressi.

Figura 7: campionamento dei degnali di ingresso, mediante utilizzo di filtri digitali che consentono di eliminare eventuali glitch e spike dovuti a rumore esterno.

Nella figura 7 si può notare che i segnali A e B (indicati rispettivamente come QEA e QEB) sono campionati utilizzando il clock Tcy. Se almeno 3 campioni consecutivi hanno lo stesso valore, allora l’uscita dell’encoder viene aggiornata, altrimenti le variazioni del segnale di ingresso sono scartate. Il segnale di clock (Tcy) può essere diviso utilizzando un prescaler (il blocco Clock Divider di figura 7) tra i seguenti possibili valori: 2, 4, 16, 32, 64, 128 e 256. Più bassa risulta la frequenza di clock selezionata, più basse saranno le frequenze di rumore tagliate. L’inserimento di questi filtri nella catena di acquisizione provoca una latenza nella risposta del decoder che comunque si può ritenere trascurabile ai fini dell’interpretazione dell’informazione. I fronti di salita dei segnali sono rilevati da un contatore dedicato a 16bit, in grado di incrementare e decrementare il suo valore. Esso è anche indicato con il nome di contatore di posizione. Per fissare un punto di riferimento per posizione e velocità, il contatore può essere azzerato sia dal segnale Z (indicato anche come INDEX) sia da un timeout impostabile. Per abilitare i filtri digitali sui canali QEA e QEB, il bit QEOUT deve essere impostato ad 1. Invece, per abilitare il filtro su INDEX si dovrà settare il bit INDOUT. A differenza degli encoder assoluti, in cui la posizione del rotore è nota a priori, negli encoder incrementali i segnali di uscita non forniscono di per se nessuna informazione sulla posizione angolare in un dato istante.

Modalità di funzionamento del decoder

Il cuore di tutto il modulo è rappresentato dal blocco Quadrature Decoder Logic, il quale ha il compito di determinare la direzione di rotazione e generare il segnale di clock che incrementerà/decrementerà il relativo contatore (16-Bit Up/Down Counter in figura 7). E’ possibile selezionare tra due diverse modalità di funzionamento:

➤ Modalità x2. Il decoder genererà solo un impulso di clock sui fronti di salita o discesa del segnale QEA.

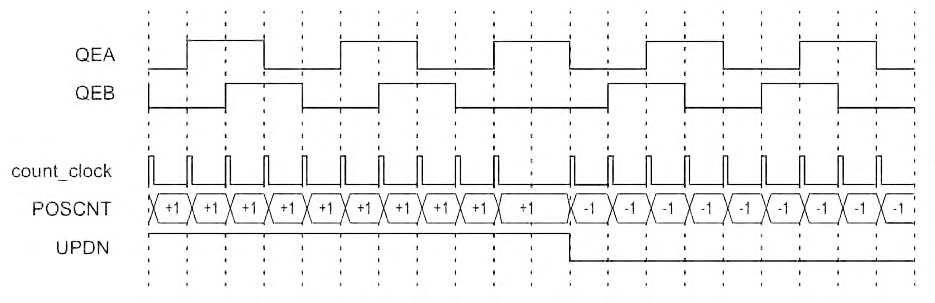

➤ Modalità x4. Il decoder genererà impulsi di clock in corrispondenza di ogni fronte (salita e discesa) e per ogni segnale (QEA e QEB). Queste modalità sono selezionata tramite i bit QEIM<2:0>, contenuti nel registro QEICON<10:8>. La posizione del contatore potrà essere azzerata sia tramite il segnale di reset del decoder sia col verificarsi della condizione di uguaglianza del Max Count Register e del 16Bit Up/Down Counter. Se QEIM<2:0> = 100 allora la posizione del contatore sarà azzerata dal segnale INDEX. Se, invece, QEIM<2:0> = 101 allora la condizione di reset sarà determinata da Max Counter. Con la stessa logica, per utilizzare la seconda modalità (x4) sarà necessario configurare QEIM<2:0> = 110 oppure 111. In figura 8 è riportato un esempio di funzionamento del decoder in modalità x4.

Figura 8: diagramma temporare del segnale (COUNT) generato dal decoder in corrispondenza dei seganli di ingresso (PHASE A e PHASE B) e con modalità di funzionamento x4.

Nella prima metà del diagramma temporale di figura 8 la fase A precede la B, quindi il rotore ruota in senso orario e il relativo contatore sarà quindi incrementato. Nella seconda metà del diagramma, invece, si verifica un’inversione di rotazione, comprovata dal fatto che ora la fase B precede la A e quindi il contatore subirà dei decrementi in corrispondenza dei fronti dei due segnali. Questo è il motivo per cui è necessario disporre di un contatore di tipo up/down. La direzione di conteggio può essere determinata leggendo il bit UPDN nel registro di controllo del QEI. In realtà è anche disponibile un pin UPDN che consente di segnalare all’esterno la direzione di movimento. Con la modalità x4 è possibile decodificare con una risoluzione angolare molto alta, ma al contempo è necessaria una frequenza di campionamento molto alta. Con la modalità x2 si dimezza la risoluzione ma anche la frequenza utilizzata. Come regola generale la massima frequenza permessa è pari ad 1/3 della frequenza di un’istruzione (Fcy).

Utilizzo del QEI con contatore a 16 bit

Qualora le funzionalità del decoder incrementale non siano richieste, il modulo QEI può anche essere configurato come semplice contatore a 16 bit di tipo up/down. Il segnale di clock può essere sia interno che esterno; in quest’ultimo caso il pin QEA sarà l’ingresso per il clock. La direzione di conteggio può essere impostata sia tramite il bit UPDN nel registro QEICON che tramite il pin QEB. Un interrupt sarà generato quando il registro raggiunge il valore impostato in Max Count Register. La figura 9 riporta lo schema funzionale del modulo.

Figura 9: schema a blocchi del decoder incrementale configurato come semplice contatore a 16 bit di tipo up/down