Una breve introduzione all’utilizzo del controller LCD a bordo dei micro AT91SAM9. I continui progressi tecnologici del settore rendono oggi possibile integrare display LCD a costi contenuti in tutte le applicazioni embedded. La maggior parte dei micro-controllori oggi disponibili integrano per questo controller dedicati.

Di seguito è descritto in particolare come interfacciare un display LCD ai dispositivi della famiglia AT91SAM9 di Atmel. Tali microcontrollori si basano su processore ARM962EJ-S, in grado di garantire capacità di calcolo di oltre 300 MIPS. L’AT91SAM9M10, ad esempio, è un microcontrollore per applicazioni multimediali che integra decoder video hardware MPEG-4/H.264, acceleratore 2D, controller LCD, interfaccia per touch-screen resistivo e per sensore di immagini, connettività USB high-speed, Ethernet 10/100 ed SDIO. Il dispositivo è ideale per applicazioni in ambito residenziale, sistemi di intrattenimento, apparecchiature medicali, terminali point-of-safe.

TIMING VIDEO PER DISPLAY TFT.

L’interfaccia host di un display TFT consiste tipicamente delle seguenti connessioni principali:

- VSync: segnale di sincronismo verticale, segnala l’inizio di un nuovo frame HSync: segnale di sincronismo orizzontale, segnala l’inizio di una nuova

- Enable: segnale di abilitazione, attivo in corrispondenza di un pixel

- Data: valore del pixel, con risoluzione dipendente dal pannello LCD selezionato.

- Clk: segnale di clock rispetto al quale sono sincroni tutti i dati ed i controlli trasferiti al pannello

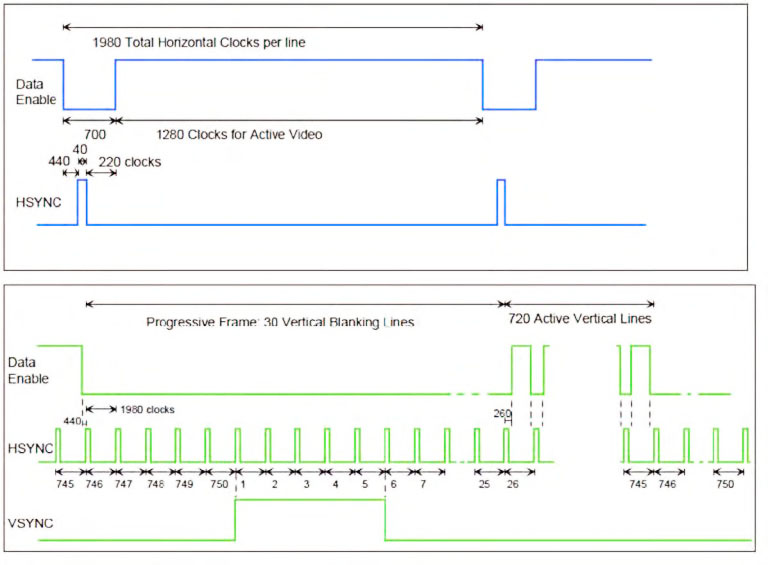

La figura 1 mostra il timing dei diversi segnali, nel caso particolare del formato 296M definito dalla specifica EIA/CEA-861-B che copre i protocolli per la trasmissione di segnali DTV non compressi.

Figura 1: timing video per display TFT (da EIA/CEA-861-B standard).

Si è assunto che i controlli siano attivi alti, ovvero che il fronte di discesa del segnale indichi rispettivamente inizio di linea e di frame. Oltre alla risoluzione dello schermo, espressa in numero di pixel per linea e numero di linee per frame, i parametri principali indicati in figura sono:

- Horizontal Back Porch (HBP): il ritardo, espresso in numero di colpi di clock Clk, tra il rilascio del controllo HSync ed il trasferimento del primo pixel valido. In altro modo, può essere inteso come il numero di pixel invalidi ad inizio

- Horizontal Front Porch (HFP): il ritardo, espresso in numero di colpi di clock Clk, tra l’ultimo pixel valido di una linea e l’asserzione del controllo HSync. In altro modo, può essere inteso come il numero di pixel invalidi a fine Horizontal Pulse Width (HPW): la durata, espressa in numero di colpi di clock Clk, del segnale di sincronismo orizzontale HSync.

- Vertical Back Porch (VBP): il ritardo, espresso in numero di linee dell’immagine, tra il rilascio del controllo VSync ed il trasferimento della prima linea contenente pixel validi. In altro modo, può essere inteso come il numero di linee invalide ad inizio frame.

- Horizontal Front Porch (VFP): il ritardo, espresso in numero di linee dell’immagine, tra l’ultima linea contenente pixel validi e l’asserzione del controllo In altro modo, può essere inteso come il numero di linee invalide a fine frame.

- Vertical Pulse Width (VPW): la durata, espressa in numero di linee dell’immagine, del segnale di sincronismo verticale VSync.

Alcuni display richiedono inoltre ritardi specifici, ancora una volta espressi in numero di colpi di clock Clk, tra il rilascio della linea VSync (ovvero l’inizio di un nuovo frame) e l’asserzione del segnale di sincronismo orizzontale HSync per la prima linea del frame. La frequenza del segnale di clock è evidentemente legata ai parametri sopra indicati ed al frame rate video. In particolare, è data da: Clk = Frame_Rate x NumLine x NumPix (1), dove: NumLine = VBP + VFP + VPW + NumActiveLine è il numero totale di linee del frame, calcolato come somma del numero di linee valide e dei parametri vertical front porch, vertical back porch e vertical pulse width. NumPix = HBP + HFP + HPW + NumActivePixel è il numero totale di colpi di clock di una linea, calcolato come somma del numero di pixel validi in essa e dei parametri horizontal front porch, horizontal back porch e horizontal pulse width. Ad esempio, facendo riferimento alla specifica 296M citata in precedenza, il formato prevede un frame rate di 50 Hz con risoluzione dell’immagine di 1280x720 pixel e pixel clock di 74,25 MHz. I parametri VBP, VFP e VPW valgono rispettivamente 5, 20, 5 mentre HBP, HFP e HPW sono invece 220, 440 e 20 per un totale quindi di 750 linee per frame e 1980 colpi di clock per linea.

CONTROLLER LCD DEI MICROCONTROLLORI AT91SAM9

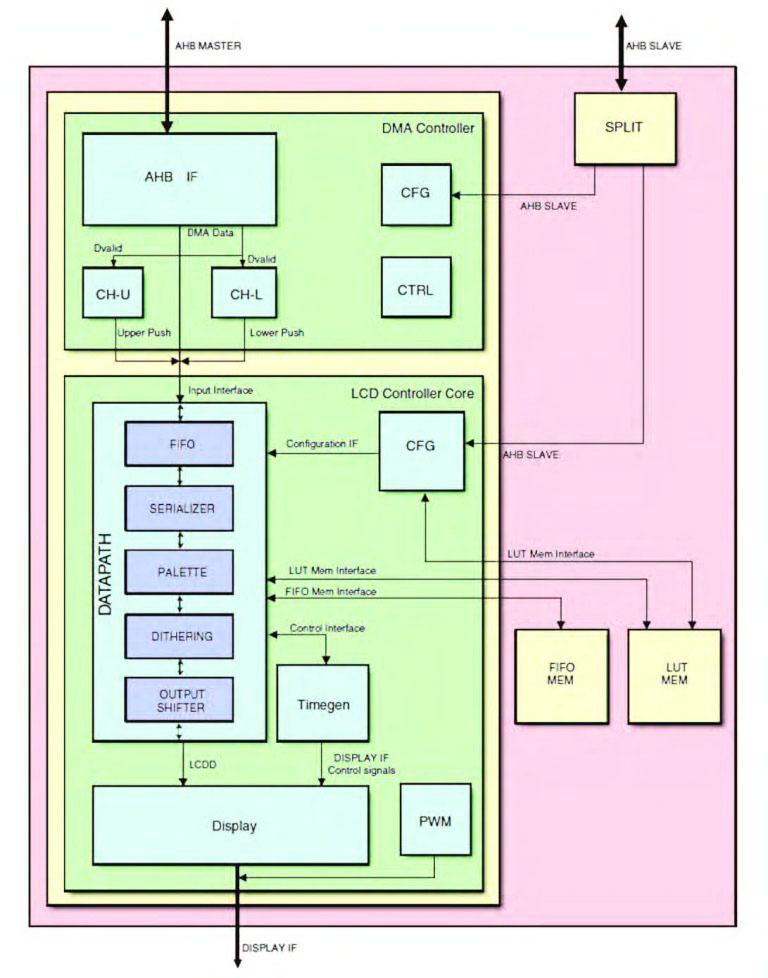

La figura 2 mostra lo schema di principio dell’architettura del controller LCD presente nei dispositivi della serie AT91SAM9.

Figura 2: architettura del controller LCD dei micro AT91SAM9.

Il controller è in grado di gestire LCD di tipo STN (Super-twisted nematic), a scansione singola o duale, a colori o monocromatici ed LCD di tipo TFT (thinf-film transistor) a colori. Nel caso di display STN, sono supportate interfacce a 4-bit a scansione singola, ad 8-bit a scansione singola o duale, a 16-bit a scansione duale. Sono implementati algoritmi di dithering time-based e frame rate control per la riduzione del flickering dell’immagine. Per i dispositivi monocromatici sono supportate fino a 16 diverse gradazioni di grigio con una risoluzione di 1 o 2 bit per pixel con uso di paletta o 4 bit per pixel in modalità senza; per i display a colori sono invece previsti fino a 4096 livelli con risoluzione di 4 bit per ogni componenti RGB. Nel caso dei display TFT, sono supportati pannelli single-scan, con fino a 16 milioni di colori (ovvero risoluzione di 24 bit per pixel) ed immagini di dimensioni fino a 2048x2048 pixel. Nel seguito ci riferiremo per semplicità alla sola gestione di tali display TFT. In questo caso, i segnali LCDDOTCK, LCDDEN, LCDHSYNC ed LCDVSYN del controller LCD riportati in figura 2 corrispondono rispettivamente alle linee Clk,Enabke, HSync e VSync descritte in precedenza. Il bus LCD[23:0] rappresenta invece il valore dei pixel. Il significato delle singole linee dipende dalla configurazione adottata; dettagli in merito si possono trovare nell’Application Note indicata nei riferimenti al punto [2]. E’ fondamentale tenere presente l’osservazione ivi espressa e relativa alla rappresentazione dei pixel in memoria in formato BGR che il controller assume, laddove la maggior parte dei layer software applicativi adotta la convenzione RGB; in caso contrario i colori sarebbe riprodotti in modo del tutto falsato. Come descritto nell’Application Note, la discrepanza può essere risolta mediante swap dei byte in software od opportuna connessione delle linee di uscita del microcontrollore al display TFT. Il controller LCD dei micro della serie AT91SAM9, come mostrato nella figura 2, consiste di due blocchi principali: il DMA controller e l’LCD controller core. Il DMA controller gestisce la lettura del valore dei pixel dalla memoria del processore, mentre l’LCD controller core, gestisce la generazione dei segnali video in accordo al formato specificato. L’LCD controller core include:

- una FIFO d’ingresso, per il buffering dei dati prelevati dal DMA Controller dalla memoria di sistema;

- un serializer, che assembla i pixel sulla base della configurazione selezionata (si veda di seguito);

- una LUT, che implementa la paletta di colori (ove tale modalità sia attiva);

- un modulo che implementa l’algoritmo di dithering (per i dettagli si veda il manuale del microprocessore indicato nei riferimenti al punto [1]);

- un generatore di timing

Il controller LCD dispone di porta AHB master per l’accesso da parte del DMA controller alla memoria di sistema tramite la matrice di switching interna per il fetch dei pixel e di interfaccia AHB slave per la configurazione dei registri di controllo.

CONFIGURAZIONE DEL CONTROLLER LCD

Tra questi vi sono i registri per la configurazione dei parametri del timing video generato dal controller. I principali sono: LCDCON1, LCDCON2, LCDFRCFG, LCDTIM1, LCDTIM2. Il primo, ovvero LCDCON1, in particolare, consente di programmare il fattore di divisione CLKVAL da applicare al clock di sistema SySClk per la generazione del clock video LCDDOTCK; la frequenza di LCDDOTCK va calcolata seconda l’espressione (1) indicata in precedenza e da questo si deriva il valore di CLKVAL mediante la seguente relazione: CLKVAL = round [SysClk /(2 x LCDDOTCK -1)] (2). Considerata l’approssimazione ad intero del fattore di divisione CLKVAL, è sempre opportuno ricalcolare, mediante la formula inversa della (2), la frequenza di LCDDOTCK che sarà generata nella pratica così da verificare che siano rispettate le tolleranze del display LCD. Il listato 1 riporta un esempio (estratto dal progetto di riferimento [3]) del codice per la sua corretta configurazione.

bpp=24; ifwidth=24; dotClockFrequency = (HORIZONTAL_SIZE * VERTICAL_SIZE * FRAMERATE * bpp ) / ifwidth ; clkval = (LCDCCLOCK / (2 * dotClockFrequency)) - 1; pLcdc->LCDC_LCDCON1 = (clkval<<12) & AT91C_LCDC_CLKVAL;

| Listato 1 |

pLcdc in questo caso è un oggetto di tipo AT91PS_LCDC, ovvero una struttura contenente l’insieme dei registri del controller LCD. Il puntatore a tale oggetto è inizializzato per puntare all’indirizzo base a cui il controller LCD è accessibile sul bus AHB. Il registro LCDCON2 consente invece di configurare il tipo di display che si intende gestire, il parallelismo dell’interfaccia di connessione, il numero di bit per pixel e la polarità dei segnali di controllo. La dimensione del frame è definita invece nel registro LCDFRMCFG mentre i parametri VBP, VFP, VPW, HBP, HFP e HPW si ritrovano nei registri LCDTIM1 ed LCDTIM2. Il campo LINEVAL di LCDFRMCFG rappresenta il numero di linee valide per frame diminuito di uno, mentre HOZVAL il numero di pixel validi per linea. Un esempio del codice sorgente per la configurazione dei registri LCDFRMCFG, LCDTIM1 ed LCDTIM2 si trova nel listato 2.

pLcdc->LCDC_LCDFRCFG = (VERTICAL_SIZE - 1) & AT91C_LCDC_LINEVAL |

((HORIZONTAL_SIZE ) << 21) & AT91C_LCDC_HOZVAL;

pLcdc->LCDC_TIM1 = VFP & AT91C_LCDC_VFP |

(VBP << 8) & AT91C_LCDC_VBP |

(VPW << 16) & AT91C_LCDC_VPW |

(VHDLY << 24) & AT91C_LCDC_VHDLY;

pLcdc->LCDC_TIM2 = HBP & AT91C_LCDC_HBP |

(HPW << 8) & AT91C_LCDC_HPW |

(HFP << 22) & AT91C_LCDC_HFP;

| Listato 2 |

Si noti come tutti i parametri da impostare sono ovviamente mascherati con le rispettive costanti che ne determinano i valori massimi supportati; prima di selezionare un tipo di pannello LCD è quindi opportuno verificare che le sue specifiche rientrino in tali valori. Oltre alla configurazione dei registri che abbiamo mostrato, l’LCD controller non richiede alcuna altra particolare inizializzazione, fatta eccezione per l’abilitazione della periferica e del relativo segnale di clock. Il listato 3 riporta le istruzioni relative.

pLcdc->LCDC_BA1 = (unsigned int)AT91C_SDRAM;

pLcdc->LCDC_FRMCFG = (VERTICAL_SIZE * HORIZONTAL_SIZE * bpp) / 32 |

((BURSTLENGTH-1) << 24);

pLcdc->LCDC_FIFO = 512 - (2*BURSTLENGTH + 3);

| Listato 3 |

TRASFERIMENTO DELLE IMMAGINI

Come accennato in precedenza, il controller LCD dispone di controller DMA per il fetch dei dati direttamente dalla memoria di sistema senza intervento del processore (fatta eccezione, ovviamente, per la programmazione del controller stesso). L’LCD controller dispone di due registri di configurazione che devono opportunamente essere programmati: il registro DMABADDR1 ed il registro DMAFRMCFG. Il primo definisce l’indirizzo base in memoria da cui iniziare a prelevare i dati. Il secondo, invece, include i campi FRMSIZE (numero di word per frame) e BRSTLN (numero di word trasferite per ogni accesso a burst alla memoria). Il numero di word per frame dipende dalla dimensione dello schermo e dal numero di bit per pixel che è stato programmato, come mostrato nel listato 3. Il registro LCDC_FIFO definisce infine la soglia di riempimento nel buffer FIFO al di sotto della quale viene automaticamente iniziato un nuovo trasferimento DMA. Nell’esempio riportato nel listato 3 si assume che il frame video da visualizzare sia memorizzato in memoria SDRAM, da dove viene anche eseguito il codice applicativo. Nella realtà si possono avere anche le configurazioni alternative in cui in cui il buffer è allocato in memoria SRAM e l’applicativo in questa stessa o nella SDRAM o, ancora (seppur meno probabile), quella in cui il buffer è allocato in SDRAM e l’applicativo esegue da SRAM. Nel caso in cui sia il buffer video che l’applicativo siano allocati nella stessa memoria, si deve tenere presente che l’accesso a questa è condiviso tra il DMA controller del controller LCD e la CPU; pertanto ci si deve assicurare che la banda di trasferimento dati garantita da tale memoria sia sufficiente. Per immagini ad elevata risoluzione la banda occupata dal DMA controller può essere piuttosto elevata; ad esempio per immagini di risoluzione 1280x720, con 24 bit per pixel e frequenze video di 50 Hz devono essere letti dalla memoria fino a circa 138 MByte/s.

L’integrazione di controller con display LCD su microcontrollori è diventata quasi prassi comune nelle applicazioni embedded. Penso alla domotica e a tutte le applicazioni nelle quali è necessario poter controllare parametri funzionali in fase operativa.