Scegliere un sistema di alimentazione per FPGA non è cosa semplice. Il tipo di applicazione, la salita monotonica dell’alimentazione del core, l’efficienza sono solo alcuni degli aspetti da tenere in considerazione.

L’impiego di una FPGA rappresenta sicuramente il sistema più flessibile e riconfigurabile per le applicazioni che vanno dal networking alle apparecchiature per telecomunicazioni a quelle industriali e per il settore automotive, e negli ultimi tempi hanno occupato anche un significativo spazio nei dispositivi consumer come i set-top box, i registratori di DVD, e i videogiochi. Il futuro della crescita delle FPGA verrà dal loro utilizzo in sistemi portatili come i GPS, le apparecchiature medicali, la strumentazione portatile, e i dispositivi consumer. Se ci chiediamo quale è la ragione che ha convinto i progettisti di dispositivi portatili a puntare la loro attenzione sulle FPGA, troviamo la risposta nei miglioramenti introdotti nei processi produttivi che hanno consentito ai costruttori di questi dispositivi di ridurre significativamente il consumo di energia, il costo e le dimensioni fisiche dei dispositivi stessi. Il proliferare delle FPGA nei dispositivi portatili ha fatto si che le problematiche legate al power management siano cresciute di importanza e rappresentino di fatto la vera sfida dal punto di vista della funzionalità ottimale del sistema. Le problematiche poste dai sistemi di alimentazione rappresentano un fattore di particolare importanza, in quanto sono strettamente legate alle caratteristiche della sorgente di alimentazione, alle complesse condizioni che si verificano al momento dell’accensione, alla risposta ai transitori, e alla corretta sequenza di applicazione delle varie tensioni. L’alimentazione delle FPGA richiede numerose sorgenti di tensione destinate al “core” (da 0,9V a 2,5V), all’I/O (da 2,5V a 3,3V), e una sorgente a basso rumore e a basso ripple per l’alimentazione dei circuiti ausiliari (tipicamente di valor compreso tra 2,5V a 3,3V). Nel caso che l’FPGA operi prelevando energia da una batteria, ai fattori appena esposti se ne aggiungono altri di importanza determinante legati all’efficienza e alla durata della batteria. Vedremo ora di esaminare alcune soluzioni avanzate per la gestione dell’alimentazione di FPGA, con particolare attenzione ai sistemi portatili che include:

- Scelte a livello di sistema per l’alimentazione ottimale di FPGA in apparecchiature portatili.

- Salita monotonica della tensione di alimentazione destinata al core dell’FPGA.

- Scalatura delle tensioni e polarizzazione del back body dell’FPGA per migliorare l’efficienza.

Scelte a Livello di Sistema

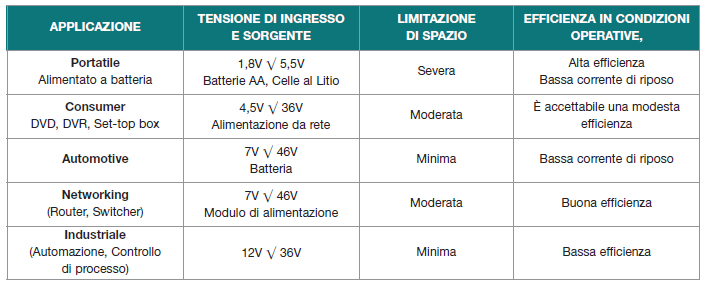

Al di là del tipo di FPGA che verrà impiegato, è l’applicazione finale a dettare le scelte relative al sistema di alimentazione. Per esempio, in un registratore per DVD completo di ricevitore satellitare sono richieste numerosissime linee di alimentazione oltre a quelle dell’FPGA. In questa specifica applicazione le dimensioni e l’efficienza dell’alimentatore non rappresentano un fattore qualificante, ma è piuttosto il costo che deve essere il più basso possibile. Di contraltare, in un sistema alimentato a batteria è l’efficienza il fattore determinante che cancella ogni altra necessità. Nella tabella 1 sono riportate alcune popolari applicazioni delle FPGA unitamente alle loro necessità di alimentazione.

Tabella 1. Condizioni di alimentazione per le più comuni FPGA

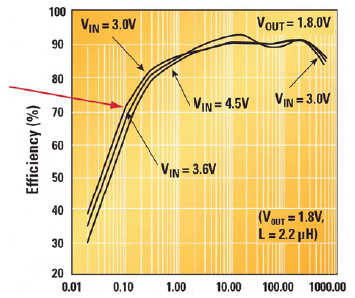

Nelle apparecchiature portatili l’efficienza sia nel funzionamento normale che nella condizione di stand-by risulta di fondamentale importanza. L’efficienza presenta un impatto diretto sulla vita utile delle batterie e quindi sul tempo di utilizzo del sistema. La tensione di ingresso di un sistema alimentato a batteria presenta valori compresi tra 1,8V e 5,5V, e la sorgente più comune è rappresentata da due celle AA o da una singola cella agli ioni di Litio la cui tensione varia tra 3V e 4,2V. Le correnti operative risultano tipicamente inferiori a 1,5A con un gran numero di applicazioni che non supera 600mA. Tenendo in considerazione che esistono consolidate linee guida per l’impiego di regolatori step-down destinati all’alimentazione di FPGA, i dispositivi portatili richiedono una elevata efficienza anche nella condizione di stand-by, per garantire la massima durata della batteria. Per questi dispositivi il convertitore buck sincrono rappresenta la soluzione ideale per alimentare le FPGA anche in condizioni di carico ridotto. In un regolatore swiching, l’efficienza a basse correnti di carico risulta piuttosto modesta, mentre sale a valori ottimali quando il carico opera a piena potenza o viene sconnesso, dato che in questa ultima condizione è possibile disabilitare il convertitore. Se stiamo alimentando una FPGA che dispone di numerose condizioni di stand-by rese possibili mantenendo attive le tensioni di alimentazione, avremo che il convertitore continua a funzionare alla stessa frequenza dissipando una inutile quantità di energia, che corrisponde a quella necessaria per operare alla massima potenza. Per superare questo inconveniente, è utile ricorrere all’impiego di un regolatore che utilizza un controllore che opera nella modalità pulse-skipping o in PFM (Pulse Frequency Modulation). Un convertitore step-down sincrono opera generalmente a frequenza fissa e in modalità continua, mentre un convertitore PFM passa dal funzionamento a frequenza variabile e tempo di conduzione fisso in condizioni di utilizzo normale, alla modalità discontinua che consente di minimizzare le perdite di commutazione, per bassi valori di corrente di uscita. All’interno di questi convertitori è presente un comparatore che campiona la tensione di uscita VO ad una frequenza fissa fPFM, e la compara con la tensione di riferimento VREF. Se VO è inferiore a VREF avremo che il convertitore genera un impulso di durata fissa per cui trasferiremo energia nella capacità di uscita. Il funzionamento PFM continua fino a che la corrente di uscita non raggiunge una specifica soglia che forza il sistema a ritornare ad operare nella normale modalità PWM. La modalità funzionale PFM presenta due consistenti vantaggi nel funzionamento a bassi valori di corrente. Il primo è rappresentato dalla sostanziale riduzione della corrente prelevata dalla sorgente di alimentazione, il secondo consiste nella riduzione delle perdite di commutazione dello stadio di uscita che viene attivato solo quando è necessario (vedi figura 1 e 2).

Figura 1. Il grafico evidenzia come il dispositivo che opera in modalità PFM presenti una elevata efficienza in tutte le condizioni di carico

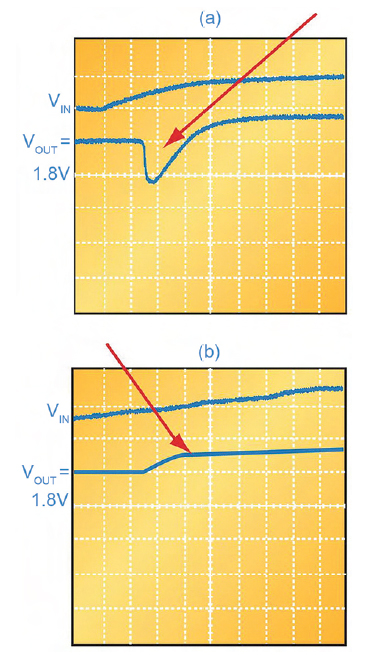

Figura 2. Salita della tensione di alimentazione non-monotonica (a) e monotonica (b)

Il progettista di sistemi di alimentazione per FPGA dovrà scegliere il dispositivo più adatto a garantire la massima efficienza sia nelle condizioni di carico nominale che di carico ridotto. Oltre a questo sarà necessario scegliere un dispositivo che presenti una bassa corrente di riposo, allo scopo di minimizzare il consumo nella condizione di stand-by.

Salita Monotonica della Tensione di Alimentazione del Core

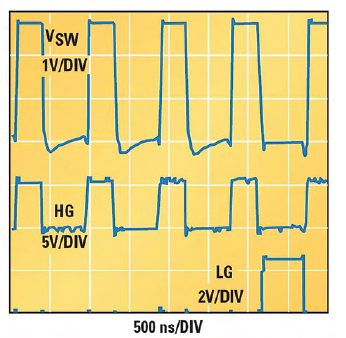

Alcuni core di FPGA e di ASIC, ma anche di alcuni processori richiedono il mantenimento di alcune tensioni durante lo shutdown. Questo genera delle condizioni di pre-bias che obbligano il convertitore a partire in condizioni anomale. Il prebias può causare anomale variazioni della tensione di uscita al momento dell’accensione, in quanto il regolatore non è progettato per operare in queste condizioni di carico. In particolare è possibile che questa tensione preesistente possa causare dei subitanei abbassamenti della tensione di uscita durante il transitorio di accensione, mentre è desiderabile che la tensione di alimentazione salga gradualmente fino a raggiungere il valore nominale. Questa condizione prende il nome di salita monotonica ed è necessaria per garantire la corretta attivazione dei vari blocchi interni dell’FPGA. Durante la salita della tensione di alimentazione avremo delle significative variazioni della corrente assorbita, per cui oltre a garantire una salita della tensione regolare, il sistema di alimentazione dovrà essere in grado di sostenere queste variazioni di corrente. Esistono due possibili approcci per garantire la monotonicità della tensione di alimentazione. Il primo consiste nell’aumentare il valore della capacità di uscita del convertitore per garantire la disponibilità di una sufficiente quantità di energia, tale da impedire variazioni di pendenza della tensione di uscita. L’aggiunta di questo condensatore impatta sia sul costo che sulle dimensioni del sistema. Il secondo approccio prevede di disabilitare il MOSFET low-side che opera come elemento di ricircolo, e monitorare il nodo di uscita durante la fase di inattività del MOSFET high-side. Il dispositivo rimane nella condizione di prebias fino a che nel nodo comune dei due dispositivi di potenza non viene rilevata una tensione inferiore a zero per l’intero ciclo di spegnimento del MOSFET high-side. Una volta raggiunta questa condizione viene attivato il normale funzionamento del MOSFET low-side. La figura 3 mostra la tensione presente sul nodo di commutazione unitamente ai segnali di pilotaggio di gate dei MOSFET high-side e low-side per un tipico convertitore sincrono.

Figura 3. Forme d’onda di commutazione durante la salita monotonica della tensione di uscita

E’ necessario che il valore della tensione di pre-bias applicata all’uscita non superi la somma della tensione di alimentazione e della tensione di soglia di gate del MOSFET high-side, allo scopo di assicurare la corretta attivazione dello stesso al momento dell’accensione.

Scalatura della Tensione per Migliorare l’Efficienza

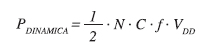

L’FPGA è essenzialmente un dispositivo CMOS soggetto ad una continua riduzione della dimensioni legata al miglioramento della tecnologia di processo. Le dimensioni dei dispositivi sono oggi inferiori ai 90nm e la frequenza di lavoro è in continuo aumento, per cui il consumo dinamico e statico diventano sempre più importanti. L’approccio attualmente impiegato per la progettazione di FPGA non consente di ottenere una semplice riduzione del consumo dinamico e statico, anche se questa è teoricamente possibile. La potenza dinamica può essere espressa in termini di numero di commutazioni N, della capacità C, della frequenza f e della tensione di alimentazione VDD:

La potenza statica, ovvero la potenza dissipata per le correnti di dispersione è riconducibile alla corrente di leakage di sub-threshold Isub, alla corrente di leakage della giunzione drain-body Ij, alla corrente di leakage della giunzione source-body Ib, ed è data dalla relazione:

![]()

dove Vbs è la tensione di polarizzazione del body. I costruttori di sistemi di potenza portatili sono giunti alla conclusione che la necessità di garanmtire una lunga funzionalità delle loro apparecchiature non può essere ottenuta semplicemente aumentando la densità di energia delle batterie o migliorando l’efficienza del sistema che la distribuisce. Per questi sistemi avanzati la “Scalatura Dinamica o Adattativa della Tensione” e il “Back Biasing” risultano essenziali per ridurre il consumo del processore. Il concetto fondamentale è derivato dall’equazione appena riportata. La strada che consente di ridurre il consumo di un processore non è costituito solo dalla riduzione della frequenza di clock , ma anche dalla riduzione della tensione di alimentazione del core al livello minimo possibile compatibile con la frequenza di clock utilizzata. Questa tecnica a spira aperta è denominata Scalatura Dinamica della Tensione (DVS). La Scalatura Adattativa della Tensione (AVS) è una tecnica di controllo ad anello chiuso che offre numerosi vantaggi nei confronti della Scalatura Dinamica della Tensione. L’AVS semplifica l’operazione di scalatura della tensione compensando automaticamente le variazioni di processo e di temperatura, ed eliminando la necessità di dover ricorrere ad una tabella frequenza-tensione indispensabile nella DVS. L’FPGA o il processore usano un sistema hardware che comunica con il controllore della potenza attraverso l’open-standard PowerWise™ Interface (PWI), e opera in modo da utilizzare la tensione minima possibile a tutte le frequenze di lavoro. La figura 4 mostra una implementazione di un sistema di scalatura avanzato.

Figura 4. Implementazione di un sistema di scalatura avanzato

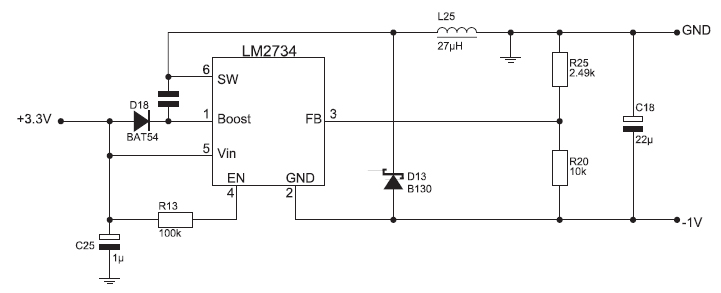

L’applicazione di una back-bias compresa tra -0,8V e -1,5V al body del FPGA, ricavata da un circuito come quello riportato nella figura 5, ci consente di aumentare la soglia dei dispositivi e ridurre il leakage di sub-threshold, ottenendo cosi una riduzione del consumo statico.

Figura 5. Circuito per la generazione di una tensione negativa da utilizzare come back-bias di un FPGA

CONCLUSIONE

Gli FPGA sono sempre più presenti nei dispositivi portatili, e al di la della necessita minimale di fornire le corrette tensioni di alimentazione, è necessario considerare l’impatto sull’efficienza e sulla durata della batteria. Un regolatore step-down in grado di garantire una elevata efficienza anche con carico ridotto rappresenta tipicamente la scelta ottimale per i sistemi portatili. Per migliorare ulteriormente l’efficienza in modo significativo è necessario fare ricorso a tecniche come la Scalatura Adattativa della Tensione. Quando la dimensione dei dispositivi scende al di sotto di 90nm diventa altrettanto importante ridurre il consumo statico dovuto all’incremento del leakage. L’impiego di dispositivi innovativi che consentano di utilizzare la tecnica di backbiasing consente di ridurre il leakage di sub-threshold e il consumo statico. Considerando che è sempre più comune la presenza di carichi prebiased nell’FPGA durante il transitorio di accensione è necessario garantire la salita monotonica della tensione di alimentazione del core per evitare possibili malfunzionamenti, utilizzando dispositivi per power management in grado di soddisfare questa necessità.