Scopriamo in questo articolo della Rubrica Firmware Reload come è strutturato, come configurare e utilizzare il convertitore analogico-digitale presente nella famiglia di microcontrollori a 8-bit della serie STM8S di STMicroelectronics.

Introduzione

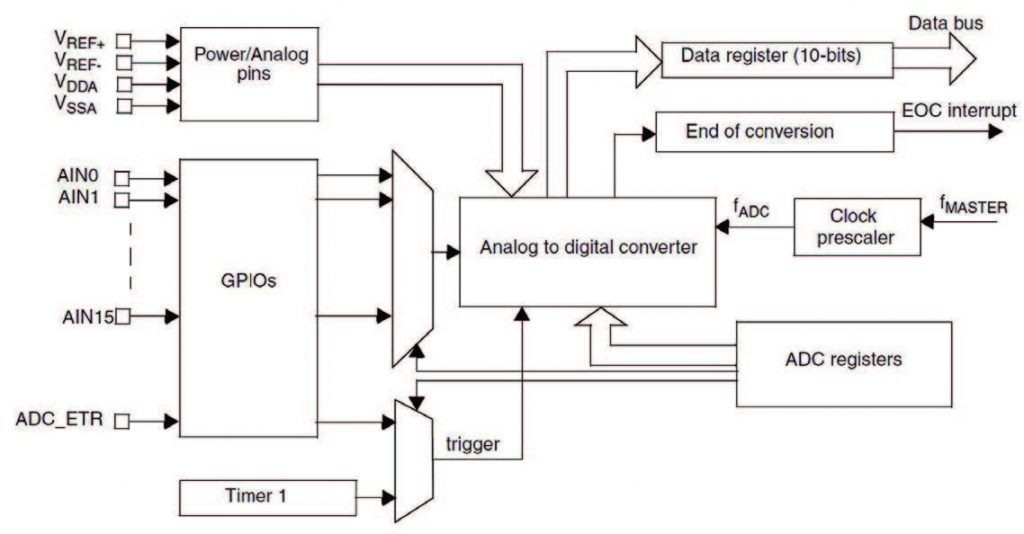

Il convertitore analogico-digitale che equipaggia la famiglia di microcontrollori STM8S dispone di 16 ingressi multiplexati ed ha una risoluzione di 10-bit. In base al particolare tipo di MCU della serie STM8, l’ADC integrato può essere del tipo base (ADC2) oppure del tipo esteso (ADC1), ed il numero di ingressi analogici esterni dipende dal particolare tipo di contenitore utilizzato. Il convertitore ADC è del tipo ad approssimazioni successive (SAR) e la conversione può essere eseguita sia nella modalità continua che in quella singola. I canali di ingresso analogici possono invece essere selezionati singolarmente oppure tramite un’opportuna scansione. Nella modalità scansione, diversi canali vengono convertiti in sequenza, ed il numero di canale selezionato viene incrementato dopo ogni conversione. Il risultato della conversione viene poi memorizzato in una coppia di registri a 8-bit. Poichè la risoluzione è di 10-bit, 6 dei 16 bit disponibili non verranno utilizzati.

Figura 1: schema a blocchi dell’ADC base

Proprio per questo scopo è disponibile un’opzione tramite la quale i 10 bit della conversione possono essere allineati a destra oppure a sinistra all’interno dei 16 bit disponibili. Il modello di convertitore ADC1 dispone inoltre di un’utile funzionalità di bufferizzazione dei dati acquisiti. Con essa, i valori di conversione prodotti dall’ADC vengono memorizzati in un numero N di buffer dati, in modo tale da ridurre il carico computazionale che grava sulla CPU. L’evento utilizzato per comandare l’inizio di una conversione analogico-digitale può essere generato con tre modalità distinte:

- evento generato a livello software;

- evento generato tramite il Timer 1 integrato nel microcontrollore STM8;

- evento generato tramite un pin esterno.

La tensione di riferimento utilizzata dall’ADC dipende dal particolare tipo di contenitore utilizzato. In particolare, possiamo distinguere due tipi di casi:

- tensione di riferimento prodotta da una sorgente esterna. In questo caso il riferimento deve essere collegato a due pin esterni;

- tensione di riferimento prodotta internamente all’MCU, e collegata ai pin di alimentazione. Il valore della tensione di riferimento VREF è limitato in ampiezza, nel senso che deve necessariamente essere compreso tra 2,75 V e VDDA. La tensione misurata, invece, deve rientrare nell’intervallo compreso tra VREF+ e VREF-.

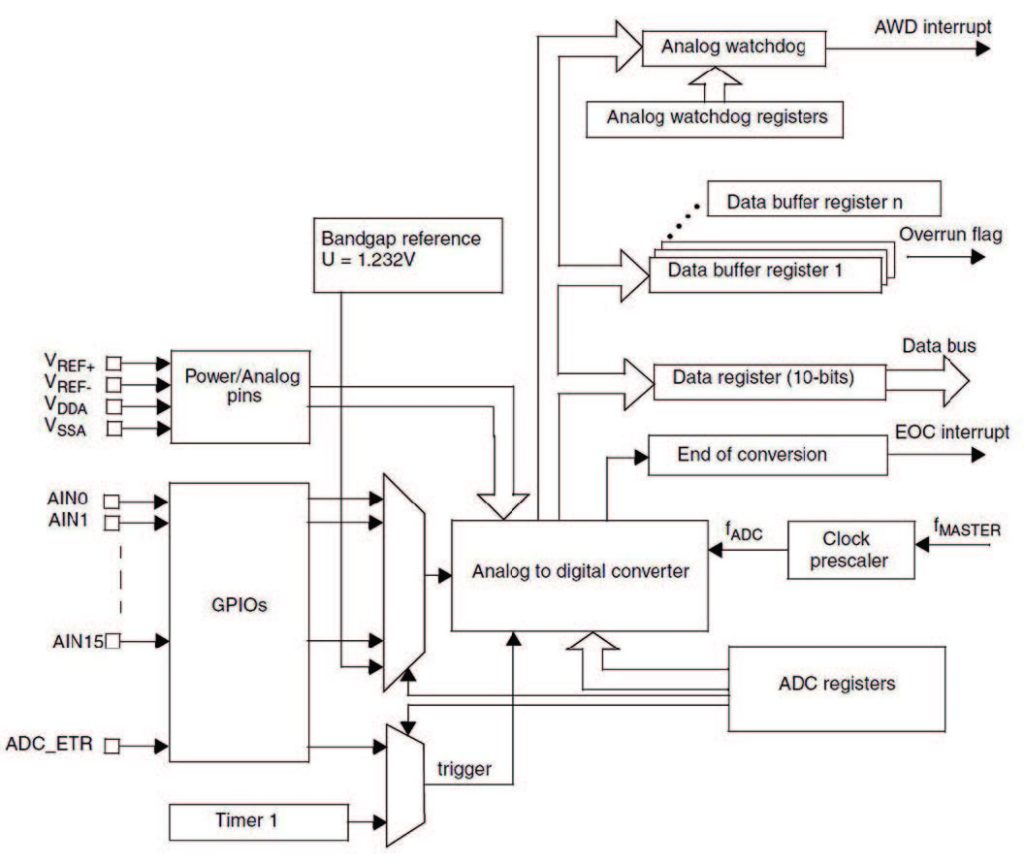

La risoluzione può inoltre essere aumentata grazie alla cosiddetta funzionalità di zoom analogico: in pratica, viene utilizzata una tensione di riferimento di ampiezza inferiore nell’intorno dei valori che si intende misurare. L’ADC di tipo esteso (ADC1) possiede anche una funzionalità di watchdog analogico, la quale confronta il dato convertito con due soglie, una inferiore e una superiore. Quando una delle due soglie viene raggiunta, viene impostata un’opportuna flag e, se abilitato, può essere generato un interrupt al termine della conversione. Il clock che comanda il convertitore analogico-digitale viene ricavato a partire dal master clock del microcontrollore tramite un divisore programmabile. Ciò consente di selezionare la velocità dell’ADC in base alle particolari esigenze dell’applicazione; la frequenza di clock fADC deve comunque avere un valore situato tra 1 e 6 MHz. La massima velocità di conversione, ottenibile con clock a 6 MHz, è pari a circa 2,33μs, corrispondenti a 14 cicli di clock. Nelle Figure 1 e 2 sono mostrati, rispettivamente, gli schemi a blocchi relativi alla versione base ed a quella estesa dell’ADC.

Figura 2: schema a blocchi dell’ADC esteso

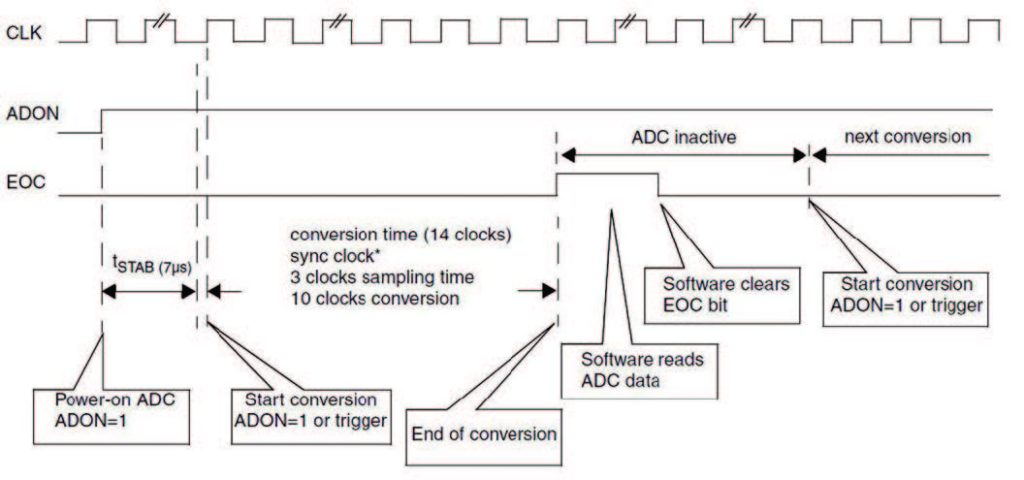

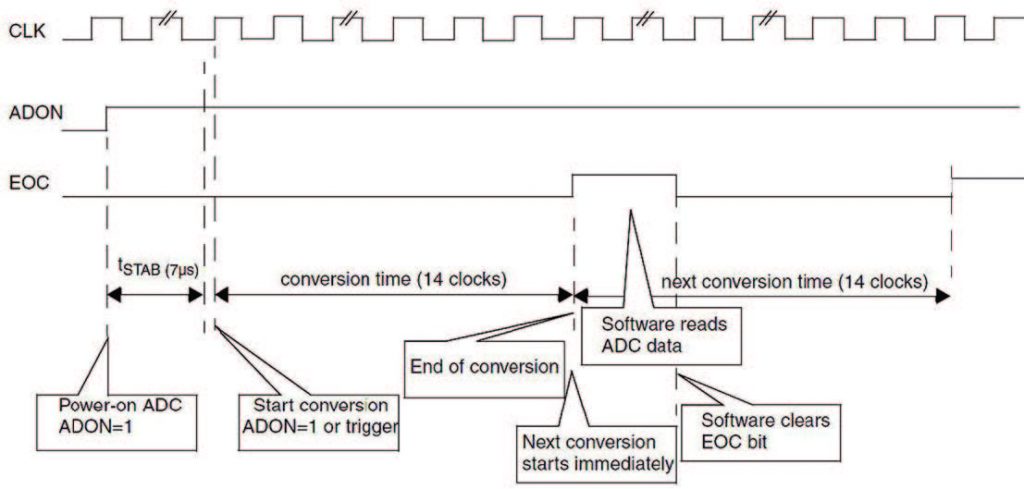

Figura 3: modo di funzionamento singolo

Figura 4: modo di funzionamento continuo

MODI OPERATIVI

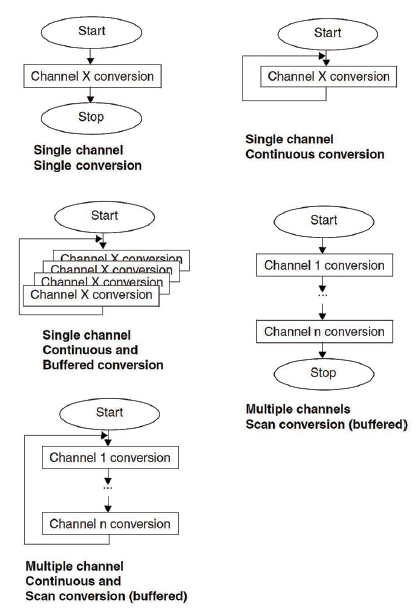

Come anticipato precedentemente, l’ADC può funzionare sia nella modalità singola che in quella continua. Nella prima, il funzionamento dell’ADC si interrompe al termine di ogni conversione, mentre in quella continua esso prosegue con la conversione successiva (eseguita sullo stesso canale oppure su canali differenti). L’andamento dei segnali significativi nelle due modalità di funzionamento è illustrato nelle Figure 3 e 4. Nel caso di ADC esteso (ADC1), le modalità singola e continua possono poi essere combinate con la funzionalità di scansione e con quella di bufferizzazione dei dati, incrementando, di fatto, il numero possibile di modalità di funzionamento come indicato in Figura 5.

Figura 5: modi di funzionamento dell’ADC1

La modalità di funzionamento singola (utilizzata ad esempio per acquisire un valore da un sensore esterno) viene programmata tramite la seguente configurazione di registri:

ADC_CR1: CONT = 0

ADC_CR3: DBUF = 0 oppure 1 se si vuole la bufferizzazione dei dati. La modalità di funzionamento continua (utilizzata ad esempio per monitorare un valore di tensione) viene attivata tramite le seguenti impostazioni:

ADC_CR1: CONT = 1

ADC_CR3: DBUF = 0 oppure 1 se si vuole la bufferizzazione dei dati

CARATTERISTICHE HARDWARE

Risoluzione

La risoluzione dell’ADC è pari a 10-bit, ma è presente una funzionalità che permette di incrementare la velocità di acquisizione dei valori convertiti a condizione di accettare una minore risoluzione degli stessi (8 bit anzichè 10). In tal caso occorre anche specificare come deve essere eseguito l’allineamento del dato convertito all’interno dei 16-bit disponibili per la conversione, programmando opportunamente il registro ADC_CR2.

Selezione del clock

Il tempo di conversione è direttamente proporzionale al segnale di clock dell’ADC, compreso tra 1 e 4 MHz oppure pari al valore fisso di 6 MHz. La frequenza di clock dell’ADC viene ottenuta dividendo la frequenza del master clock, ottenuta tramite la programmazione del registro ADC_CR1.

Trigger di conversione

La conversione può essere attivata dall’evento TRGO associato allo scadere del Timer1, oppure da un fronte di salita che si verifica sul segnale esterno ADC_ETR. E’ altresì possibile iniziare una nuova conversione via software, impostando a 1 il bit ADON del registro ADC_CR2. Le corrispondenti impostazioni dei registri sono le seguenti: ADC_CR2: bit EXTSEL e EXTTRIG ADC_CR3: DBUF = 0 oppure 1 se si vuole la bufferizzazione dei dati.

Velocità di conversione

La velocità di conversione può essere scelta all’interno del range compreso tra fMASTER/2 e fMASTER/18, dove fMASTER rappresenta la frequenza del clock interno del microcontrollore. Il registro di selezione del divisore di clock è ADC_CR1. ADC_CR1: impostare i bit SPSEL[2:0] per selezionare la velocità di conversione.

Tensione di riferimento

La tensione di riferimento deve essere collegata ai pin esterni oppure, in molti tipi di contenitore, è collegata internamente all'alimentazione. Il minimo valore della tensione di riferimento è pari a 2,75V, ed il suo valore deve essere compreso nel campo della tensione di alimentazione.

Selezione del canale di ingresso analogico

L'ADC della serie STM8 dispone fino a 16 canali di ingresso, collegati ai pin di ingresso GPIO (su alcuni dispositivi della stessa serie può comunque essere presente un numero inferiore di pin). I pin utilizzati come canali di ingresso all'ADC devono essere configurati come ingressi fluttuanti, e su tali ingressi il trigger di Schmidt deve essere disattivato, riducendo in tal modo l'assorbimento di corrente. La selezione dei canali di ingresso viene eseguita agendo sul registro ADC_CSR. ADC_CSR: selezionare i canali di ingresso impostando i bit CH[3:0]

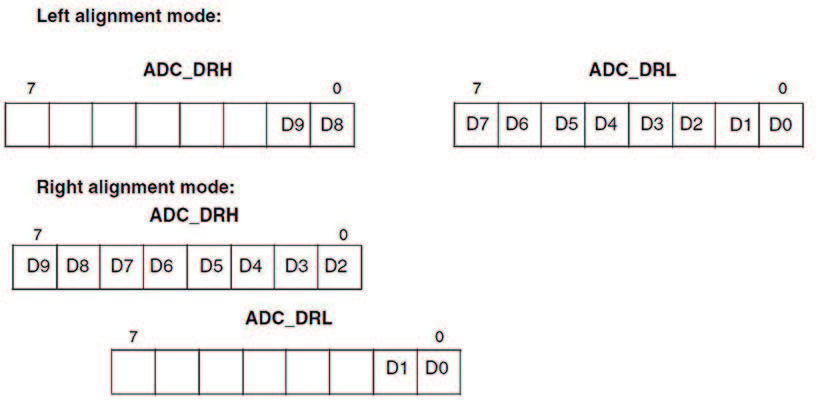

Allineamento dei dati

Il valore a 10-bit prodotto dalla conversione viene memorizzato all'interno di una coppia di registri a 8-bit (o anche, nel caso dell'ADC1, in appositi registri buffer) ed è possibile selezionare la modalità di allineamento di questo valore, come indicato in Figura 6.

Figura 6: allineamento dei dati

Affinché il dato letto dai registri sia consistente, occorre eseguire la lettura secondo un ordine particolare, a seconda del tipo di allineamento selezionato. Più precisamente, se l'allineamento è a destra, occorre leggere prima l'LSB e poi l'MSB, mentre se l'allineamento è a sinistra si legge prima l'MSB e poi l'LSB. Dopo aver letto il primo dei due byte, l'hardware congela in un registro "ombra" il valore presente sul secondo byte (anche se nel frattempo si è reso disponibile un nuovo valore di conversione) in modo tale da garantire sempre delle conversioni consistenti.

Gestione degli interrupt

Le sorgenti di interrupt dell'ADC sono selezionabili tra uno o più dei seguenti tipi di eventi:

- fine della conversione (EOC) in modalità non bufferizzata, generato al termine di ogni conversione analogico-digitale;

- fine della conversione (EOC) in modalità bufferizzata, generato quando i registri buffer contengono tutti dati validi e una nuova scrittura causerebbe un over-run dei registri;

- alert proveniente dal watchdog analogico, generato quando i valori convertiti superano la soglia inferiore oppure superiore. L'utilizzo di eventi consente di ottenere un elevato livello di efficienza a livello software.

Quando il programma principale è in esecuzione, i cambiamenti di stato della conversione gli vengono notificati tramite appositi eventi, senza necessità di dover campionare continuamente il loro stato. Ad esempio, abilitando l’interrupt di fine conversione, è possibile leggere immediatamente l’ultimo dato di conversione disponibile senza dover campionare la flag di stato della conversione. Il registro da impostare è il seguente: ADC_CSR: bit AWDIE e EOCIE.

FUNZIONI ESTESE

Le funzioni estese descritte nel seguito sono disponibili soltanto sulla versione ADC1 del convertitore.

Bufferizzazione

Quando questa funzionalità viene attivata, i dati convertiti vengono memorizzati ciclicamente in appositi registri buffer, gestiti come un vero e proprio buffer circolare. Ciò rende l’acquisizione e la memorizzazione dei dati molto più efficiente, in quanto è richiesta una minore disponibilità di CPU e gli over-run (sovrascritture) dei buffer vengono ridotti. Il numero di registri buffer è uguale al numero di canali dell’ADC, il quale, a sua volta, dipende dal particolare tipo di dispositivo della serie. Nel caso in cui i dati presenti nei buffer vengano riscritti senza essere stati precedentemente letti, viene alzata automaticamente la flag di over-run: il firmware utente può quindi utilizzare questa flag per rilevare un evento di over-run e intraprendere le azioni conseguenti (ad esempio, far ripartire la conversione A/D). I registri e i bit significativi per impostare questa funzionalità sono i seguenti:

ADC_CR3: bit DBUF

ADC_CR2: bit ALIGN

ADC_CR3: bit OVR

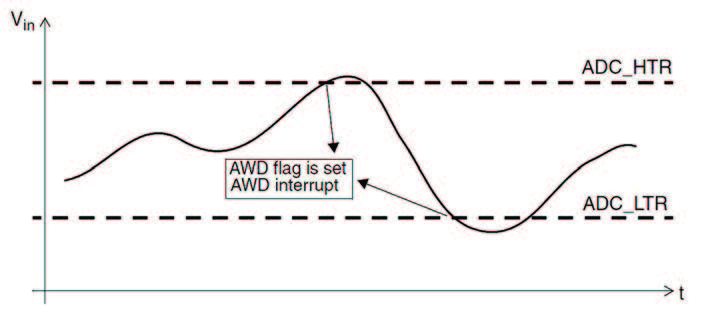

Watchdog analogico

Questa funzionalità confronta l’ultimo valore convertito con due soglie, una inferiore e una superiore (si veda la Figura 7).

Figura 7: watchdog analogico

Se una delle due soglie viene raggiunta o superata, viene alzata un’apposita flag e generato un interrupt. In questo modo è così possibile controllare dei valori critici per la conversione (generando ad esempio un allarme quando viene superata una determinata soglia) senza perdere tempo prezioso di CPU. I registri da impostare per attivare questa modalità sono:

ADC_HTRH, ADC_HTRL, ADC_LTRH, ADC_LTRL – soglie inferiore e superiore ADC_AWCRH, ADC_AWCRL – registri di controllo ADC_AWSRH, ADC_AWSRL – registri di stato ADC_CSR: bit AWDIE e AWD

Modalità scansione

Questa funzionalità permette di eseguire delle conversioni su canali consecutivi. Quando è terminata la conversione sul canale n-esimo, viene selezionato come canale di ingresso il canale (n+1)-esimo, e la conversione successiva verrà eseguita su di esso. La sequenza di scansione deve sempre partire dal canale 1, e procede in sequenza fino al canale N (programmabile). Quest’ultimo viene impostato selezionando opportunamente i bit di selezione del canale di ingresso. Quando la modalità scansione è combinata con la modalità continua, terminata l’acquisizione dal canale N, la scansione riparte dal canale 1, e il ciclo si ripete indefinitamente. La modalità viene attivata agendo sui seguenti registri:

ADC_CR2: set del bit di SCAN

ADC_CR3: DBUF = 0 oppure 1 se si vuole la bufferizzazione dei dati. Nel caso in cui vengano utilizzati i registri buffer dati (DBUF=1), i dati convertiti vengono memorizzati nei registri ADC_DBXRH e ADC_DBXRL che compongono il buffer circolare, anzichè nei registri non-bufferizzati ADC_DRH e ADC_DRL.

CONCLUSIONI

Abbiamo visto in questo articolo le funzionalità caratteristiche del convertitore analogico-digitale presente sulla serie di microcontrollori STM8S (sia nella versione base che in quella estesa). Abbiamo anche fornito dei dettagli su quali registri utilizzare, e come impostarli, per attivare i modi di funzionamento desiderati. Per chi volesse approfondire l’argomento, ricordiamo che sul sito STMicroelectronics (http://www.st.com) è liberamente disponibile la libreria firmware completa per l’STM8, contenente numerosi esempi completi di codice sorgente, tra cui appunto l’ADC.