Con la serie Virtex-5, Xilinx continua a percorrere la strada dei multi-platform FPGA integrando core hard IP in dispositivi logici riprogrammabili di nuova generazione. I componenti delle serie LXT ed SXT, in particolare, includono macro tri-mode ethernet mac (media access control) 10/100/1000 MBPS IEEE 802.3 compliant. Il presente articolo ne introduce le caratteristiche principali unitamente ad una panoramica delle tipiche applicazioni supportate.

Nel mercato moderno, Ethernet è, senza ombra di dubbio, lo standard di connessione cablata più diffuso al mondo; allo stesso modo, nel settore delle applicazioni embedded i dispositivi logici programmabili rappresentano ormai una consolidata realtà in rapida diffusione. Non era difficile prevedere, quindi, che le due soluzioni avrebbero finito presto per convergere in una piattaforma comune. Nel 2007, Xilinx ha iniziato la produzione di massa dei dispositivi della serie Virtex-5, multi-platform FPGA caratterizzate da logica ad elevate prestazioni, connettività seriale high bit-rate, capacità DSP e supporto per applicazioni embedded. I componenti della serie LXT ed SXT in particolare integrano – come i predecessori della famiglia Virtex-4 FX – macro hardware che realizzano un MAC Ethernet per applicazioni 10/100/1000 Mbps. Unitamente ai transceiver Rocket-IO GTP ed alla tecnologia SelectIO, Xilinx rende in questo modo disponibile una soluzione single-chip per connessioni in rete estremamente flessibile, facile da utilizzare, ad elevate prestazioni e bassa dissipazione di potenza.

L’architettura del core

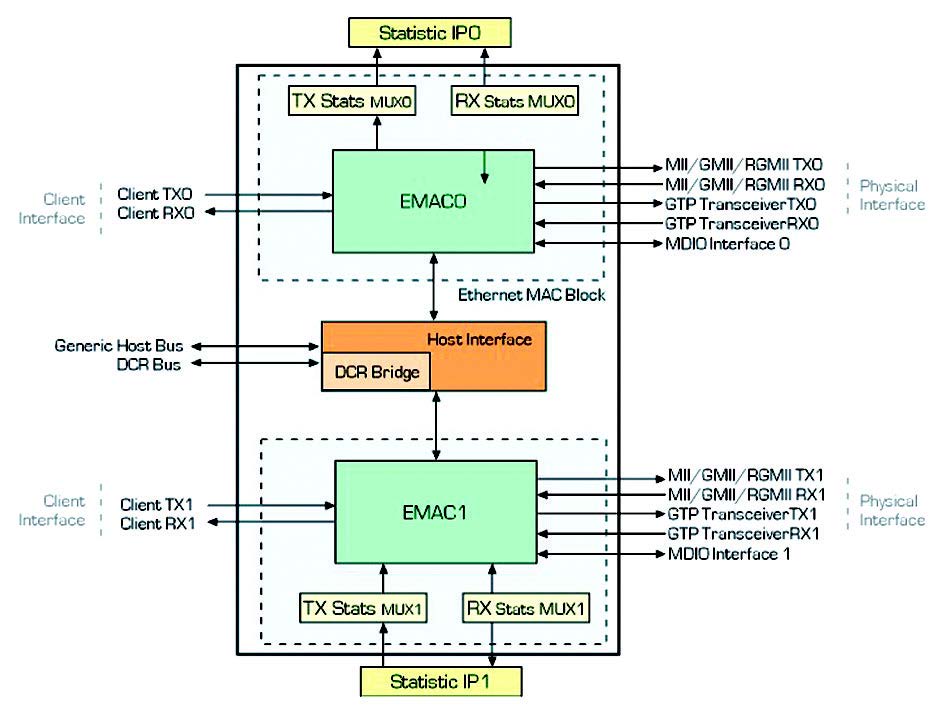

La figura 1 mostra uno schema a blocchi di un core TEMAC (Tri-Mode Ether net MAC) il quale include due macro Ethernet MAC (EMAC) identiche e che condividono una comune interfaccia verso il processore host per la configurazione; sono invece indipendenti le porte di trasmissione e ricezioni dati in modo da consentire comunicazioni full-duplex su entrambi i canali.

Figura 1: L’architettura della macro TEMAC (da: Virtex-5 Embedded Tri-Mode Ethernet MAC User Guide)

Il core è configurabile in modalità full-duplex con bit-rate 10/100/1000 Mbps ed half-duplex 10/100 Mbps; è inoltre disponibile una modalità di overcloking che consente trasmissioni fino a 2,5 Gbps per applicazioni su backplane seriali. Una porta di comunicazione two-wire standard MDIO (Management Data Input/Output) consente l’accesso ai registri di configurazione di un eventuale componente esterno che implementi il layer fisico del protocollo o della sezione PCS/PMA del MAC Ethernet nelle configurazioni seriali del core in connessione ai transceiver GTP. L’interfaccia host per la configurazione può essere di tipo generico, tipicamente nelle applicazioni in cui il core è direttamente controllato da una applicazione host di tipo custom realizzata in FPGA, o compatibile con le specifiche del protocollo DCR dell’architettura per bus on-chip IBM CoreConnect in connessione ad un processore embedded. Sono supportate fino a cinque diverse interfacce fisiche. MII (Multimedia Independent Interface), GMII (Gigabit Multimedia Independent Multimedia Independent Interface) sono, ad esempio, protocolli paralleli fino a 1 Gbps per accesso ai dispositivi esterni che implementino una connessione di tipo Base-T per trasmissione su mezzi in rame. SGMII (Serial Gigabit Multimedia Independent Interface) è, invece, una interfaccia di tipo seriale utilizzata in alter nativa alla configurazione GMII/MII per ridurre il numero di pin di I/O necessari, in maniera da semplificare, per certi versi, il progetto del circuito stampato; utilizza i transceiver GTP Rocket IO per la serializzazione del dato in trasmissione. Su di essi è basata anche la con figurazione 100-BaseX che implementa i layer PCS (codifica del dato in insiemi ordinati, encoding 8b/10b, autonegoziazione per lo scambio di informazioni con il nodo partner) e PMA (serializzazione dei code-groups, clock recovery) del protocollo Ethernet MAC. Si è in grado in questo modo di realizzare una soluzione single-chip con connessione diretta, ad esempio, a transceiver ottici di tipo GBIC (Gigabit Interface Converter) o SFP. La figura 2 mostra uno schema di maggiore dettaglio dell’architettura interna di ognuno dei due moduli EMAC integrati in una macro TEMAC.

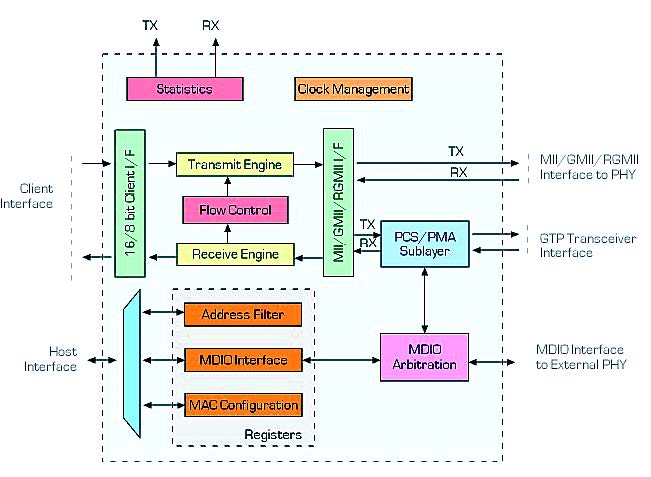

Figura 2: L’architettura del core EMAC (da: Virtex-5 Embedded Tri-Mode Ethernet MAC User Guide)

Vi è, come si può notare, una interfaccia client a 16 o 8 bit connessa ai motori di trasmissione e ricezione dati su Ethernet. L’interfaccia a 8 bit è utilizzata, ad esempio, nelle classiche configurazioni; quella a 16 bit è, invece, disponibile per le sole applicazioni 100BASE-X e, unitamente ad una modalità di overclocking del core, permette comunicazioni fino a 2.5 Gbps, come già anticipato. In trasmissione, il core implementa automaticamente il padding dei dati alla lunghezza minima specificata per un frame, controlla la minima distanza tra frame configurata e, qualora sia abilitata, introduce le sequenze di controllo; in modalità half-duplex, inoltre, segnala le situazioni di collisione richiedendo, nei casi validi, la ritrasmissione del frame. In ricezione è invece inclusa una funzionalità di filtro degli indirizzi che consente di selezionare i frame da trasferire all’applicazione client in base all’indirizzo di destinazione. Possono essere rilevati un indirizzo programmabile in trasmissioni di tipo unicast, fino a 4 indirizzi programmabili generici, frame di tipo broadcast o di controllo di pausa; in questo modo l’interfaccia client può essere protetta da traffico estraneo riducendo l’overhead di trasferimento dati sul bus di sistema e di esecuzione dei task. È inoltre supportato un meccanismo di controllo di flusso mediante scambio di frame di pausa. Il MAC, infatti, può essere configurato in modo da sospendere l’invio di dati per il periodo di tempo specificato nel messaggio ricevuto in modo da evitare eventuali errori di overflows dei buffer del nodo ricevente.

Per cominciare…

Come evidenziato nel paragrafo precedente, la macro TEMAC è un componente piuttosto complesso con 162 porte e 79 parametri di configurazione. Per fater no delle applicazioni finali, Xilinx rende disponibile all’interno del Core Generator un V i rtex-5 Embedded Tr i-Mode Ether net MAC Wrapper che consente la generazione automatica di wrapper files, test-bench e progetti di riferimento per le configurazioni selezionate dall’utente. I test-bench sono basati su un modello SmartModel (modello comportamentale distribuito in formato binario con interfaccia procedurale) del core TEMAC supportato dai principali ambienti di simulazione attualmente più diffusi sul mercato (tra i quali, ad esempio, ModelSim di MentorGraphics).

Il livello più basso (Embedded Ethernet MAC Wrapper) è rappresentato dalla configurazione del core TEMAC in base alle esigenze dell’utente; quindi sono istanziati i transceiver Rocket I/O per le interfacce fisiche che lo richiedano ed i circuiti di distribuzione del clock (buffer ed eventuali DCM). L’interfaccia client è di tipo generico; include memorie FIFO di 4 Kbyte in ricezione e trasmissione. La comunicazione con l’applicazione host per i dati è su bus LocalLink, un protocollo ad elevate prestazioni introdotto da Xilinx come interfaccia utente per interconnessioni a livello sistema tipicamente in applicazioni system-on-chip. Nel progetto di riferimento, l’applicazioni host è un semplice esempio di loop-back; il frame ricevuto viene spedito invertendo indirizzi sorgente e destinazione. L’esempio può facilmente essere sintetizzato in ISE e scaricato su una scheda di valutazione per verificar ne il funzionamento.