L’ EBM in un modulo definito standalone che rende disponibile al microcontrollore, su dei pin dedicati, una serie di I/O general purpose e un expansion bus per tutta la famiglia di questo fortunato microcontrollore. Il modulo supporta, poi, il multiplexing. Questo modulo permette, quando i canali di I/O non sono utilizzati, di interfacciare, attraverso il microcontrollore, memorie con taglio a 8 e 16 bit.

Caratteristiche principali

L’EBM, come abbiamo scritto, permette di fare il multiplexing dei segnali di I/O verso una periferica ed è in grado di interfacciare memorie con taglio a 8 e 16 bit. Permette, inoltre, di indirizzare periferiche fino a 30 bit di indirizzo con 8 bit di dati o fino a 22 bit di indirizzo per 16 bit di dati. Possiamo così riassumere le sue caratteristiche:

➤ un bus dati a 8 o 16 (EBDATA[7:0] o EBDATA[15:0]);

➤ fino a 2 write strobes;

➤ fino a 4 chip selects;

➤ 1 output enable;

➤ 1 external hold signal per interfacciare memorie lente;

➤ permette di gestire fino a 8 DMA.

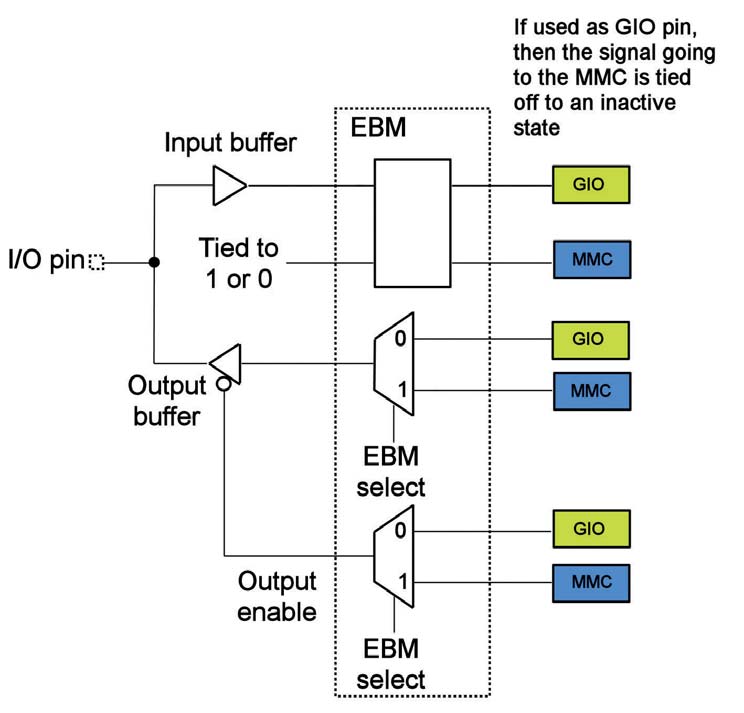

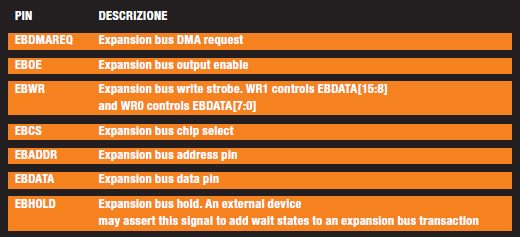

La figura 1 mostra il diagramma dell’EBM, mentre la tabella 1 pone in evidenza i segnali dell’EBM con una loro breve descrizione.

Figura 1: il diagramma dell’EBM.

I registri dell’ebm

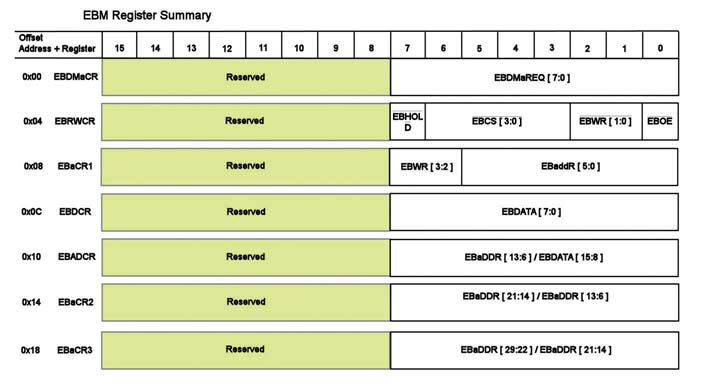

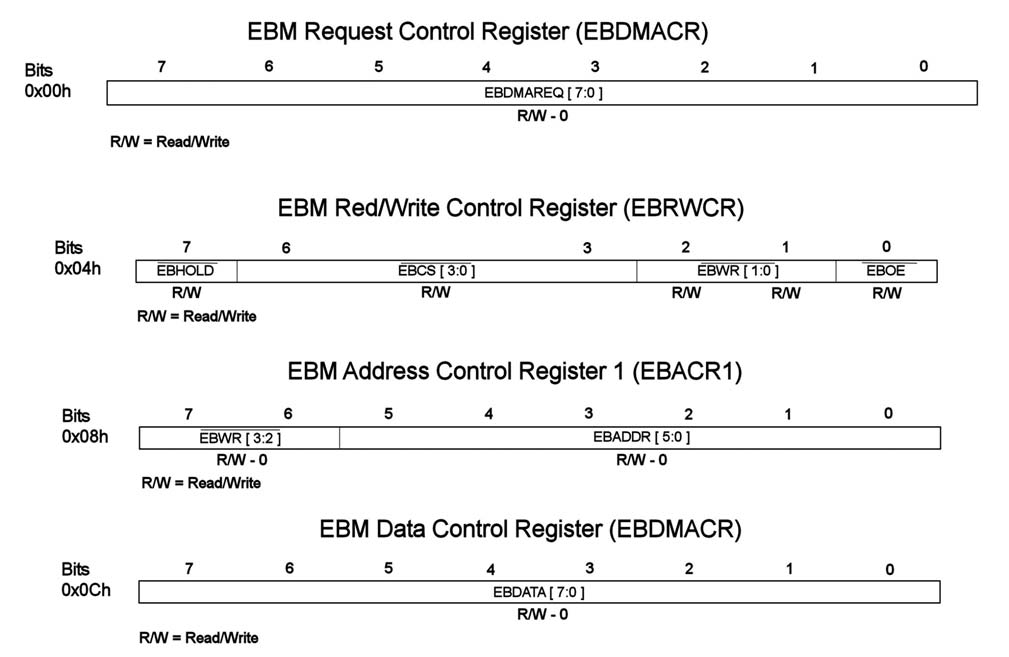

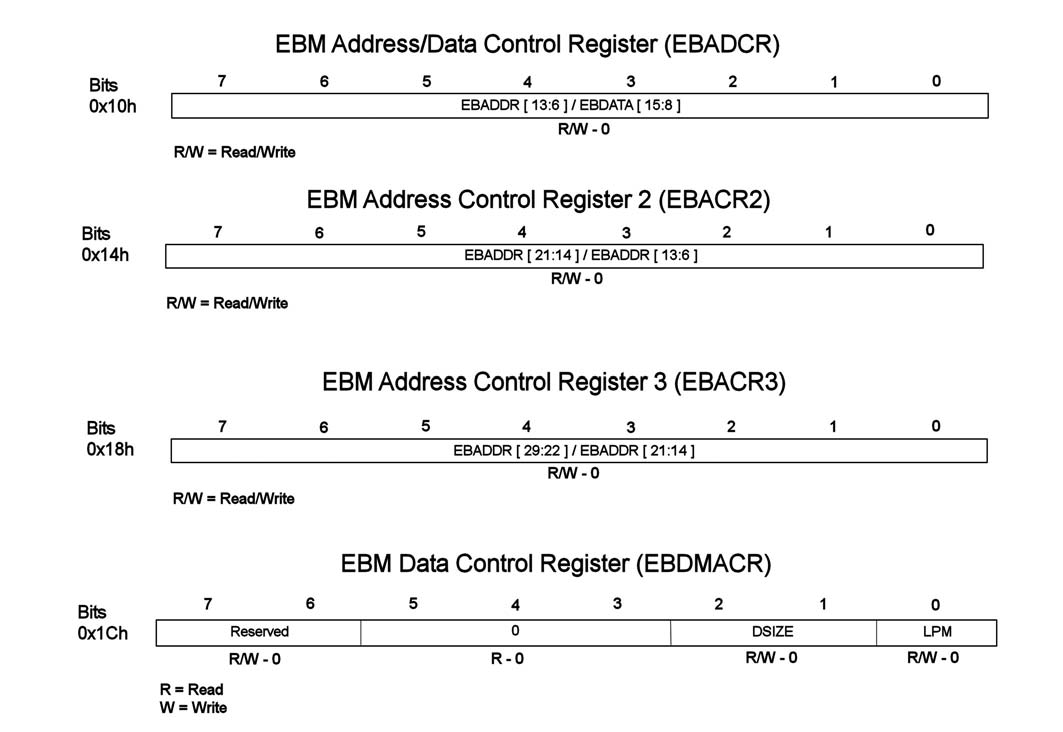

La figura 2 mostra i registri dell’EBM con il significato dei singoli bit, insieme alle figure 3 e 4. È bene precisare che la scrittura su qualsiasi di questi registri non ha effetti sui 16 bit più significativi.

Figura 2: i registri dell’EBM con il significato dei singoli bit.

Figura 3: i registri dell’EBM con il significato dei singoli bit.

Figura 4: i registri dell’EBM con il significato dei singoli bit.

Esempio pratico: interfaccia verso una memoria esterna

In questo esempio solo, sono menzionati i registri pertinenti del modulo EBM. Per descrivere l’esempio occorre definire le seguenti due asserzioni:

➤ una memoria, con bus dati di 16 bit, con una capacità di indirizzamento fino a 64Kb è connessa al chip select 5;

➤ Il chip select 5 è relazionato con MCBAHR2/MCBALR2 e SMCR5.

Per implementare questa interfaccia occorre mettere a punto la seguente procedura:

■ 1-Il primo passo deve riguardare la configurazione del clock di sistema. Per fare questo occorre scrivere nel registro GLBCTRL un valore appropriato; nel nostro esempio la scrittura è:

GLBCTRL = 0x09

■ 2-Il secondo passo è quello di mettere un valore appropriato nei re gistri MCBAHRx e MCBALRx. In questo modo si seleziona il corretto base address per il chip select connesso al modulo Expansion Bus Multiplexer (EBM) per pilotare la memoria o una periferica esterna. Per fare questo occorre abilitare la mappa di memoria, in questo modo:

//EBM base address della memoria

// all’indirizzo 0x00300000

MCBAHR2 = 0x0030;

// Taglio di 64 Kb di memoria

MCBALR2 = 0x0020;

// Abilita la mappa di memoria,

// ora è possibile accedere

// correttamente al

// segmento di memoria definito

// precedentemente

MFBALR0 = 0x0100;

■ 3-A questo punto dobbiamo utilizzare il registro SMCR. Come ultimo passo dobbiamo definire il segmento appena inizializzato come esterno e associare il relativo wait states, se necessario perché dipende dal tipo delle memorie utilizzate. Per esempio:

//La seguente scrittura

//definisce una memoria esterna

//a 16 bit, di tipo big endian e

//con 3 wait states

SMCR5 = 0x35;

■ 4-Occorre configurare ICLK per la periferica. Per esempio:

PCR = 0x02

■ 5-Resettiamo la periferica. Per resettare la periferica interveniamo sempre sul registro PCR, in questo modo:

// Abilita la periferica

PCR |= 0x01

■ 6-A questo punto non ci rimane altro che inizializzare iI registro del modulo EBM. Occorre, infatti, configurare il data bus utilizzando il registro EBMCR1, inizializzare le linee di controllo e di dati richieste dal modulo EBM nei registri di controllo associati. Possiamo riassumere tutto questo attraverso questa sequenza di inizializzazione:

EBDMACR = 0x01;

EBRWCR = 0x0F;

EBACR1 = 0x3F;

EBDCR = 0xFF;

EBADCR = 0xFF;

EBACR2 = 0xFF;

EBACR3 = 0x07;

EBMCR1 = 0x02;

■ 7-Come ultima cosa occorre considerare il DMA. Se risulta necessario utilizzare il DMA per il trasferimento dei dati, allora occorre inizializzare in maniera appropriata il registro EBM che si occupa del componente. Il registro in questione è EBMDMAREQx, abilitando i canali DMA interessati. Questa che abbiamo illustrato è la sequenza corretta per utilizzare l’EBM nel caso in cui volessimo utilizzare una memoria esterna. È chiaro che i valori dei registri citati dipendono dalla tecnlogia della memoria utilizzata e del sistema a contorno. Per particolari usi, per esempio sul wait states, può essere utile consultare il documento della Texas Instruments siglato SPNU189. Inoltre, risulta necessario consultare il data sheet di ogni singolo componente per valutare il relativo, per esempio, bus timing. Come ultima considerazione, penso che occorre fare una piccola nota sul wait states e sulle periferiche associate. Quando, per esigenze progettuali, dobbiamo interfacciarci verso dispositivi di memoria lenti rispetto alla velocità della CPU occorre senza dubbio inserire degli stati di wait per sincronizzare le operazioni. Come abbiamo visto precedentemente, la configurazione di questi stati di attesa sono fatte scrivendo degli opportuni valori nel registro SMCR. Tutto cambia se, invece, avessimo a che fare con delle periferiche esterne lente. In questo caso per ottimizzare le prestazioni, le letture verso questi dispositivi devono essere accompagnate dal segnale di EBHOLD della periferica per generare il wait state appropriato. Chiaramente, non tutte le periferiche generano questo segnale o, al contempo, la periferica non consente di utilizzare una logica esterna programmabile, allora, a questo punto, è necessario che la generazione degli stati di wait debba essere fatta dalla CPU, alla stessa stregua delle interfacce verso memorie esterne.

Temporizzazione

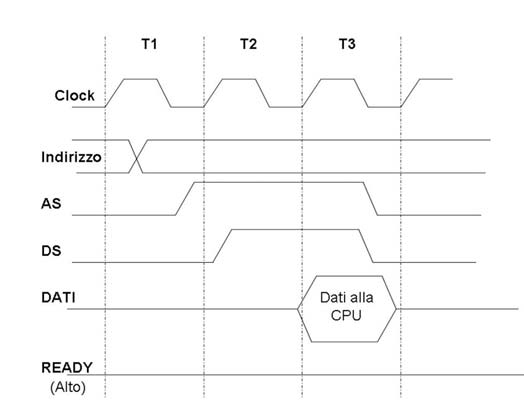

Vediamo, per i neofiti, cosa si intende per wait states, e lo facciamo ricorrendo ad un esempio. In questo esempio, ci riferiremo ad un’ipotetica CPU. Consideriamo, quindi, una ipotetica sequenza di temporizzazione di un ciclo di lettura dalla memoria. Un ciclo di questo tipo e può richiedere, per esempio, tre cicli di clock che corrispondono a tre stati: T1, T2 e T3. Vediamo le transizioni dei segnali in questi tre ipotetici cicli (figura 5).

Figura 5: le transizioni dei segnali nei cicli.

■ T1) In questa prima parte è necessario che la CPU ponga l’indirizzo della locazione da leggere sulle linee di indirizzo. La CPU attende, per un breve intervallo, che le transizioni dei segnali si stabilizzino e, di conseguenza, rende alto il segnale di abilitazione dell’indirizzo (AS), in questo modo la memoria può partire con le sue operazioni inter ne. Tutto questo avviene se l’indirizzo è valido con le informazioni di controllo che la memoria ha ricevuto. In definitiva, lo stato T1 deve consentire alla CPU di trasmettere alla memoria tutti i segnali di controllo richiesti per l’operazione di lettura.

■ T2) La fase T2 è possibile dividerla in due sottofasi. Durante la prima parte, la CPU rende alto il segnale di abilitazione del dato (DS). Questo vuole dare una indicazione alla memoria: la CPU è in attesa del dato di lettura prima della fase T3. Però questo non vuol dire che la memoria è in grado di fornire il dato secondo la tempistica dettata dalla CPU. Lo stato T2 serve alla CPU per trasmettere il segnale DS alla memoria e per esaminare la linea READY.

■ T3) Il dispositivo periferico, la memoria, pone sul bus dati l’informazione letta dalla locazione indirizzata dalla CPU. Questa viene letta dalla CPU sul fronte di discesa del segnale DS e la linea AS viene disattivata. La memoria rilascia il bus dopo il fronte di discesa di DS. A questo punto l’attività in T3 è quella di leggere e terminare la sequenza di temporizzazione. Ma che cosa succede se la memoria non è sufficientemente rapida da fornire il dato in tempo? Occorre portare la linea READY nello stato basso prima del fronte di discesa di T2. La CPU deve allungare il ciclo di macchina per dare alla memoria più tempo per completare l’operazione di lettura. L’allungamento si ottiene inserendo degli stati di attesa: cicli di clock durante i quali la CPU non deve fare assolutamente nulla e servono semplicemente affinchè la memoria completi l’operazione. In sostanza la sequenza descritta è ancora valida, ma con piccoli aggiustamenti. Sul fronte di discesa di T2, la CPU deve prendere nota che il segnale READY si trova nello stato basso. Al termine di T2, la CPU non procede con T3, ma entra in uno stato di attesa; in questo modo, comunque, la CPU non conosce se uno stato di attesa sia sufficiente. Per essere sicuro di questo, la CPU deve riesaminare la linea READY sul fronte di discesa del wait states, lo stato inserito tra T2 e T3. Se READY è alto, la CPU entra in T3 al completamento del wait states, altrimenti inserisce un nuovo stato di attesa.

Tabella 1: descrizione dei Pin dell’EBM.

Conclusione

L’uso dell’EBM permette, senz’altro, di ottimizzare le nostre realizzazioni e di aggiungere flessibilità alle nostre applicazioni. L’uso di questo modulo, per chi non è più giovane, può ricordare il microcontrollore MC68332; infatti, questo microcontrollore permetteva di gestire e selezionare chip select verso una periferica esterna e impostare gli appropriati wait states.