L’ADuC7022 appartiene alla serie di microcontrollori analogici di precisione ADuC7xxx basati su core ARM-TDMI a 32 bit RISC e integranti un ADC 12-bit multicanale ad elevate prestazioni, Flash/EE memory on-chip e numerose altre risorse hardware. Come gli altri modelli della sua famiglia può essere considerato un ottimo componente per lo sviluppo di applicazioni mixed-signal.

I microcontrollori ADuC di Analog Devices combinano funzioni analogiche di precisione, grazie ad ADC e DAC ad alta risoluzione, con risorse fisiche quali riferimento di tensione, sensore di temperatura e porte di interfaccia che li rendono particolarmente adatti per impieghi in svariate applicazioni sia specifiche, come in campo industriale, medicale ed automotive che nel campo delle telecomunicazioni e più in generale consumer. Tra le diverse famiglie di controllori Analog troviamo quelli della serie ADuC7xxx ARM7TDMI® composta da modelli che integrano convertitori A/D a 12, 16 e 24-bit e DAC a 12-bit. Nel proseguo dell’esposizione faremo riferimento prevalentemente al modello ADuC7022, tuttavia molto dei con tenuti che esporremo valgono anche per gli altri modelli della famiglia ADuC7xxx.

ADUC7022: ARCHITETTURA GENERALE

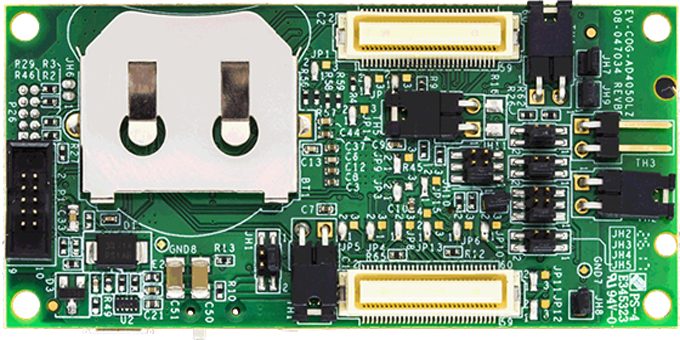

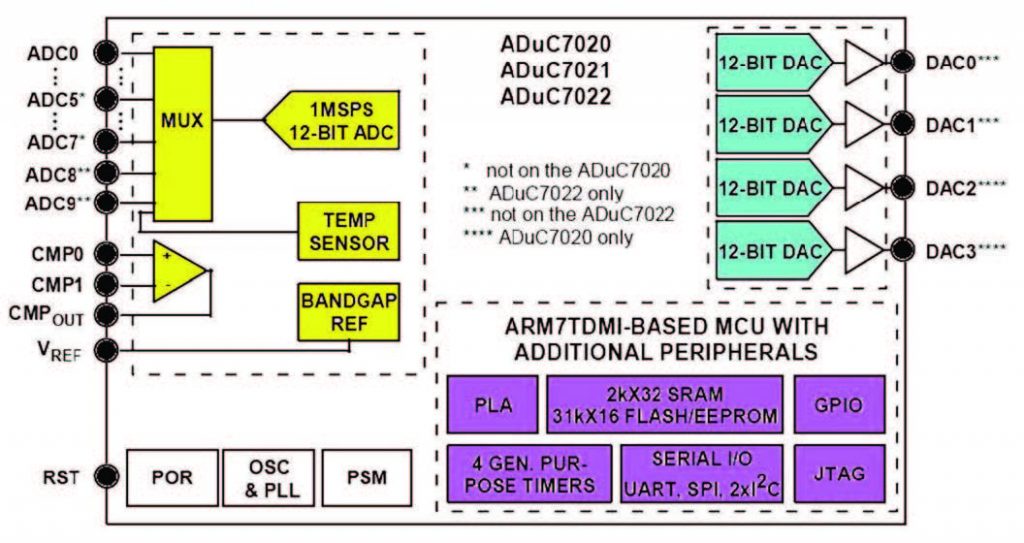

Il chip ADuC7022, come gli altri microconverter ADuC7xxx della Analog Devices si presenta come un componente ottimo per lo sviluppo di applicazioni mixed-signal embedded. La velocità di campionamento fino a 1MSPS, l’integrazione di ADC a 12 bit e di una MCU a 16bit/32bit basata su core ARM7-TDMI RISC e la memoria flash embedded rende gli ADuC7xxx adatti sia allo sviluppo di applicazioni embedded di medio livello che di alto livello. Il banco di ADC del modello ADuC7022 comprende complessivamente 10 A/D converter. La serie ADuC7xxx integra anche una serie di DAC tranne che per alcuni modelli tra cui l’ADuC7022 (figura 1).

Figura 1: architettura generale dei chip ADuC7020/21/22.

Gli ADC possono operare sia in modalità single-ended che in modalità differenziale, come avremo modo di illustrare meglio successivamente. L’ingresso dell’ADC può variare nel range 0-Vref. Il riferimento di tensione a band-gap, un sensore di temperatura ed un comparatore completano la sezione periferica ADC del chip (figura 1). Il microcontroller è basato su core ARM7TDMI®, 16-bit/32-bit RISC, funziona con alimentazione compresa tra 2.7 V e 3.6 V (e temperatura comprese tra −40°C e +125°C). Come in tutti i casi in cui si debbano valutare le potenzialità applicative di un chip è necessario ed opportuno esaminarne per prima cosa l’architettura interna ed il pin-out. L’anello di congiunzione tra le due cose è costituito dalla periferiche di interfaccia verso l’esterno e dalle alimentazioni. La figura 1 riporta l’architettura generale del chip e ne evidenzia sia le risorse fisiche che le interfacce verso il mondo esterno.

PIN-OUT E PACKAGE

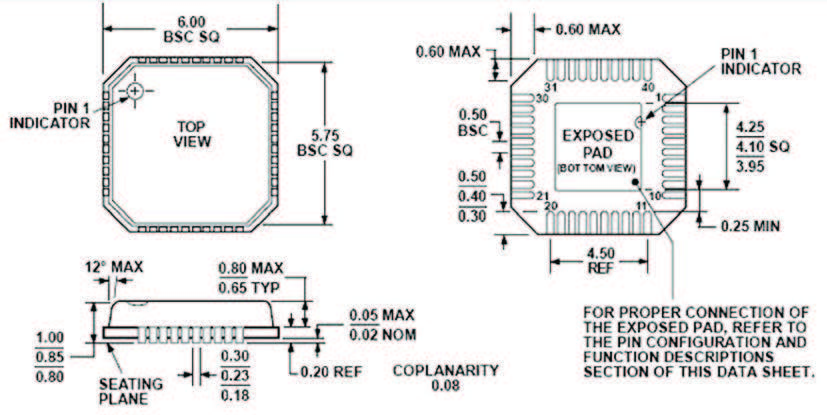

L’analisi del pin-out di un chip insieme a quella della sua architettura e delle sue risorse fisiche consente di comprenderne le potenzialità applicative. In figura 2 sono riportati i dettagli dimensionali che riguardano il package del chip e dai quali se ne deduce l’enorme compattezza a dispetto dei suoi 40 pin complessivi. Nella successiva figura 3 è invece riportata il pin-out dello stesso chip.

Figura 2: package LFCSP_VQ 40 pin del chip ADuC7022 (si notino le dimensioni estremamente contenute: 6mmx6mm).

Figura 3: pin out del chip ADuC7022 (package LFCSP_VQ).

L’ARCHITETTURA ARM

Si è già detto che l’ADuC7022, come gli altri modelli della stessa serie di controllori, si basa sull’architettura ARM. E’ opportuno allora soffermarci su alcuni aspetti sia storici che tecnici che riguardano la nascita e l’evoluzione di questa architettura. L’architettura ARM (precedentemente Advanced RISC Machine, prima ancora Acorn RISC Machine) è una architettura RISC a 32-bit sviluppata da ARM Holdings e molto utilizzata nei sistemi embedded. Grazie alle elevate prestazioni ed alle caratteristiche di basso consumo l’architettura ARM domina soprattutto il settore dei dispositivi mobili dove il risparmio energetico è fondamentale (cellulari, lettori multimediali, videogiochi portatili e periferiche per computer, router, hard disk di rete ecc). Il progetto ARM risale al 1983 ad opera della Acorn Computers Ltd. Il primo prototipo prese il nome di ARM1 (1985) ma il primo processore realmente prodotto fu sviluppato solo dopo con il nome ARM2. Si trattava di un processore con bus dati a 32 bit e bus di indirizzi a 26 bit. All’epoca l’ARM2 era il più semplice processore a 32 bit poiché con soli 30.000 transistor era più semplice del Motorola 68000 che ne aveva 68.000, pur garantendo prestazioni simili. Il processore doveva la sua semplicità alla mancanza di microcodice che invece nel 68000 occupava praticamente un quarto del numero complessivo di transistor. Come la maggior parte delle CPU dell’epoca non era dotata di cache, risorsa che fu presto aggiunta con l’introduzione del successivo ARM3 che venne dotato di 4KB di cache. Alla fine degli anni 80 Apple computer iniziò a lavorare con Acorn per sviluppare una nuova versione del core ARM cui fu preposta la Advanced RISC Machines Ltd. Per questo motivo spesso ARM viene inteso come Advanced RISC Machine invece che Acorn RISC Machine. Nacque così ARM6. L’idea di base del progetto riguardava il core del processore e mirava a permettere agli OEM di combinarlo con vari componenti opzionali per ottenere una cpu completa, economica ed a basso consumo. Seguì l’implementazione di maggior successo ARM7-TDMI prodotta in centinaia di milioni di esemplari e che caratterizza gli ADuC7xxx. Agli ARM7 TDMI si sono successivamente aggiunte le evoluzioni ARM9TDMI, ARM10, ARM 11 e Cortex con prestazioni sempre migliori. L’architettura ARM è in ogni caso un’architettura RISC che include:

- architettura load/store;

- mancato supporto ad accessi alla memoria non allineati (supportati dal core v6);

- set di istruzioni ortogonale; # ampi registri a 16/32 bit;

- istruzioni a lunghezza fissa che semplificano la decodifica e l’esecuzione a costo di diminuire la densità del codice;

- esecuzione in un ciclo di clock per la maggior parte delle istruzioni.

Per competere con processori dell’epoca come l’Intel 80286 e il Motorola 68020 l’architettura prevedeva alcune caratteristiche uniche tra cui quella dell’esecuzione condizionata di molte istruzioni per ridurre i salti e compensare gli stalli della pipeline. Con 4 bit addizionali si realizzavano infatti codici condizionali per ogni istruzione. Questi codici consentivano in pratica di evitare i salti nei caso di semplici “if”. Un’altra caratteristica unica del set di istruzioni è la capacità di shiftare i dati durante le normali operazioni sui dati (operazioni aritmetiche, logiche e di copia di registri). Queste caratteristiche rendono i programmi ARM capaci di determinare un accesso alla memoria meno frequente e di riempire in maniera più efficace le pipeline. Questa particolarità consente alle CPU ARM di lavorare a frequenze inferiori rispetto ad altri processori comportando di conseguenza un minor consumo di potenza a parità di prestazioni complessive. I primi processori ARM7 erano basati su un disegno con pipeline a 3 stadi: fetch, decode e execute. I processori più moderni come l’ARM9, per incrementare le prestazioni sono passati a pipeline a 5 stadi. Gli ultimi processori ARM sono inoltre dotati di un set di istruzioni a 16 bit chiamato Thumb. Nonostante il codice Thumb sia dotato di minor funzionalità, è più leggero e soprattutto nel caso di sistemi dotati di limitata larghezza di banda verso la memoria fornisce prestazioni migliori del set di istruzioni completo. In queste situazioni conviene creare codice Thumb per la maggior parte del programma e ottimizzare le parti di codice che richiedono molta potenza di calcolo utilizzando il set di istruzioni completo. Il primo processore dotato di Thumb è stato proprio l’ARM7-TDMI. Tutti gli ARM9 e le famiglie successive (incluso gli XScale) sono dotati di Thumb. ARM Ltd non produce in realtà la proprie CPU e non vende dispositivi basati sulle sue CPU ma licenzia ad altre aziende la possibilità di realizzare CPU basate su core ARM.

ARM7-TDMI

L’ARM7 e un core a 32-bit di tipo RISC (Reduced Instruction Set Computer). Esso impiega uno stesso bus a 32 bit per istruzioni e dati. I dati possono presentare lunghezza sia ad 8 che a 16 o 32 bit mentre la lunghezza dell’istruzione è pari a 32 bit. L’ARM7-TDMI è invece qualcosa di più in quanto presenta quattro caratteristiche aggiuntive da cui deriva l’acronimo TDMI e che possono così essere riassunte:

T:Thumb (16 bit) instruction set;

D: support for debug;

M. support for long multiplies;

I: EmbeddedICE

(debugging embedded).

Dettagli specifici e più approfonditi sull’architettura ARM possono essere consultati sul seguente documento facilmente reperibile in rete: DDI0029G, ARM7TDMI Technical Reference Manual. Analizziamo più in dettaglio le quattro caratteristiche aggiuntive.

THUMB MODE (T)

Un istruzione ARM è lunga 32 bit. Un ARM7-TDMI supporta un set di istruzioni di questo tipo ma supporta anche un secondo set di istruzioni compresse in soli 16-bits noto con il nome di Thumb Instruction Set. L’impiego di questo set di istruzioni consente esecuzioni più veloci e maggiore densità di codice rispetto all’uso del set di istruzioni ARM classico. Questa è la caratteristica fondamentale che rende il core ARM7-TDMI particolarmente adatto allo sviluppo efficiente di applicazioni embedded ad elevate prestazioni. Ovviamente, questo aspetto non comporta unicamente conseguenze positive ma anche qualche limite: in particolare il funzionamento in Thumb mode presenta due principali inconvenienti:

- il codice che impiega il Thumb set normalmente necessita di un maggior numero di istruzioni per eseguire lo stesso algoritmo;

- il Thumb instruction set non comprende alcune istruzioni necessarie per il trattamento delle eccezioni. Di conseguenza il vantaggio è soprattutto nelle performance che derivano in termini di tempo di esecuzione di parti critiche dello stesso codice e questo aspetto è molto sfruttato soprattutto nei sistemi embedded.

LONG MULTIPLE (M)

Il set di istruzioni ARM7-TDMI comprende quattro istruzioni extra che consentono di eseguire moltiplicazioni tra operandi a 32 bit ed operazioni di moltiplicazione 32-bit con 32-bit con accumulo (MAC - Multiplication - Accumulation) con il risultato memorizzato in un registro a 64-bit. Il vantaggio di tutto ciò sta nel fatto che tali operazioni vengono eseguite in meno cicli macchina rispetto a quanto richiesto in un core ARM7 standard.

EMBEDDEDICE (I)

Il chip supporta la modalità Embedde-dICE (In-circuit emulation) on-chip. In altre parole supporta il debugging embedded grazie alla presenza di registri di breakpoint e watch-poinit che consentono di mettere in stato di stop il flusso esecutivo del codice per FINALITà di debugging. Questi registri sono controllati attraverso porta di interfaccia JTAG. Quando si incontra un breakpoint oppure un watchpoint il processore blocca l’esecuzione del codice ed entra in stato di debug. In questo stato il contenuto dei registri del processore può essere analizzato e la stessa cosa può essere fatta sulla Flash memory, sulla SRAM e sui registri mappati in memoria (MMR- Memory Mapped Register).

I REGISTRI DEL CORE ARM7-TDMI

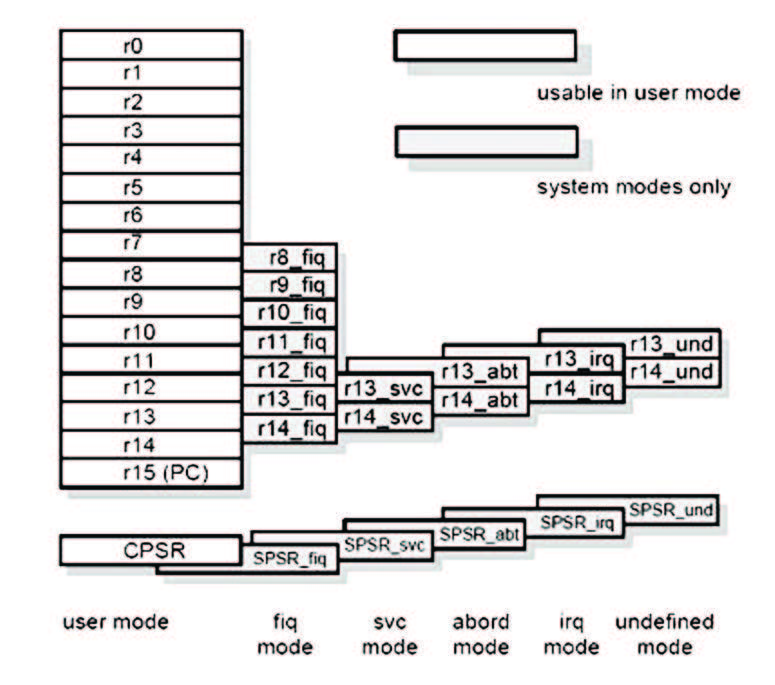

Il core ARM7-TDMI integra complessivamente 37 registri di cui alcuni possono essere considerati di tipo general-purpose e altri di stato (status registers) (figura 4).

Figura 4: organizzazione dei registri.

Tra questi ultimi si nota in particolare il registro CPSR (Current Program Status Register). I primi 15 in particolare (r0..r14) sono general-purpose, r15 rappresenta il Program Counter (PC) mentre i rimanenti sono invece utilizzati principalmente per la gestione delle eccezioni.

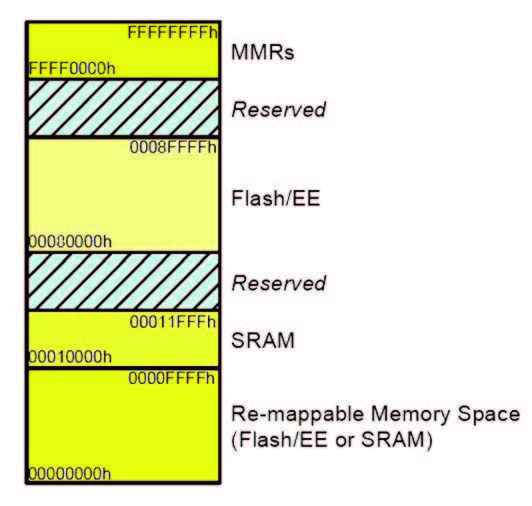

ORGANIZZAZIONE DELLA MEMORIA

Tutti i chip ADuC702x integrano due blocchi distinti di memoria: 8 kB di memoria SRAM e 64 kB di memoria Flash/EE on-chip. Di questo secondo blocco 62 kB Flash/EE sono riservati all’utente. La figura 5 schematizza la mappa di memoria fisica del controllore.

Figura 5: organizzazione della memoria dei chip ADuC702x.

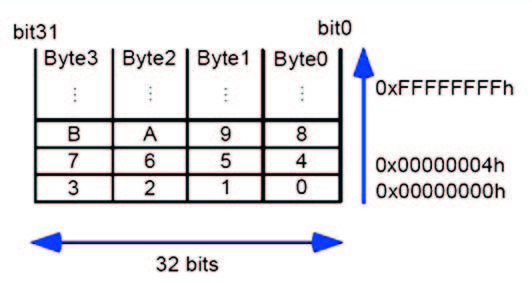

Entrando più nello specifico, la memoria Flash è organizzata come memoria a 32k X 16 bit cioè 32k locazioni da 16 bit. Di questo spazio fisico 31k X 16 bit (cioè 31k locazioni da 16 bit) rappresentano spazio utente mentre 1k X 16 bit sono riservati alle funzioni di bootloader. All’interno della memoria non c’e distinzione tra memoria di programma e memoria dati. In ogni caso la memoria è gestita a 16 bit e questo implica che per ciascuna operazione di instruction fetch sono necessarie due accessi successivi alla memoria Flash/EE. Questo spiega perché per ottimizzare le prestazioni è opportuno impiegare il chip in Thumb mode (cioè fare uso del Thumb instruction set). Quanto detto spiega perché mentre la velocità di accesso alle istruzioni presenti nella Flash memory è pari a 45MHz in Thumb mode, la stessa si dimezzi a 22.5MHz in full ARM mode. Come mostra la figura 5, la memoria è nel suo complesso un array di 232 locazioni di memoria. L’organizzazione della memoria rispecchia il formato little endian, il che significa che il byte meno significativo corrisponde all’indirizzo di memoria più basso mentre quello più significativo corrisponde all’indirizzo di memoria più alto (figura 6).

Figura 6: formato Little Endian.

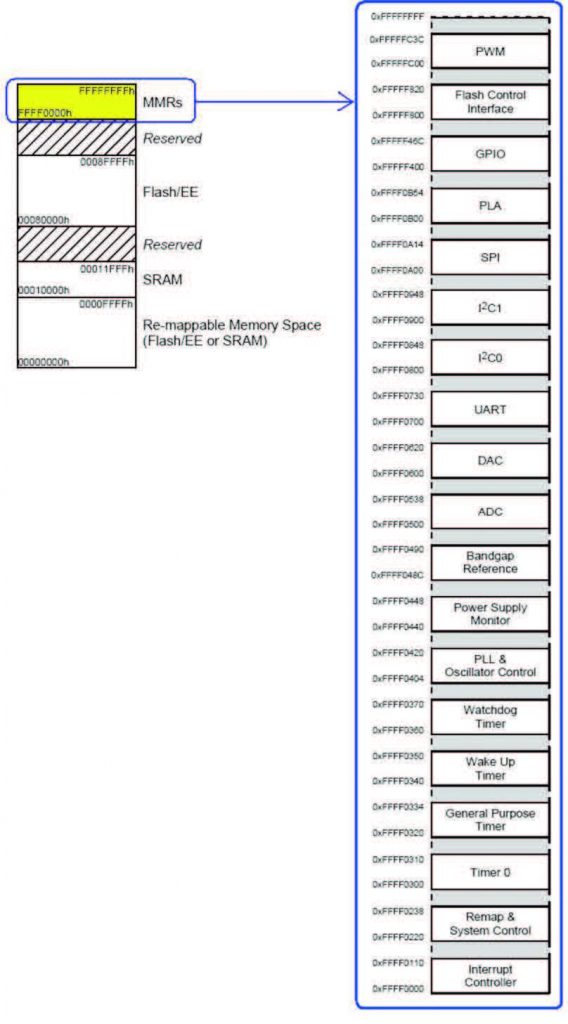

SRAM

8kBytes DI SRAM sono disponibili per l’utente organizzati in 2k word da 32 bit ciascuna (2k X 32bits). Tutti i registri ad eccezione dei core register sono contenuti nella MMR (Memory Mapped Register), sono cioè mappati all’interno della memoria Flash nella porzione che va dall’indirizzo FFFF0000h all’indirizzo FFFFFFFFh. La figura 7 evidenzia quanto appena esposto.

Figura 7: area di memoria riservata ai registri MMR (Memory Mapped Register).

Ciascuno dei segmenti all’interno dell’area MMR è a sua volta suddiviso ulteriormente per categorie di registri. Per esempio, il segmento FFFF0000h…FFFF0110h (Interrupt Controller) comprende diversi registri (IRQSTA, IRQSIG, ecc…). Per chi voglia approfondire l’argomento e conoscere nel dettaglio i registri che compongono i diversi segmenti rimandiamo allo studio diretto dei datasheet dei singoli componenti ADuC7xxx tra cui segnaliamo quelli riportati nella sezione “Riferimenti bibliografici”.

LA SEZIONE DI CONVERSIONE ANALOGICO/DIGITALE (ADC)

L’architettura di un controllore, in generale, è sufficiente a rendere l’idea delle sue potenzialità applicative, soprattutto se confrontata con quella di altri analoghi dispositivi. Capita allora che determinati chip siano privilegiati dalla disponibilità di determinate risorse fisiche e di interfaccia piuttosto che altre. Questo comporta un orientamento applicativo preferenziale che lo contraddistingue. Per questo motivo è necessario, nello sviluppo di una qualunque applicazione embedded a microcontrollore, individuare prima di tutto la categoria di microcontrollore da utilizzare in base agli specifici orientamenti applicativi, quindi individuare all’interno della categoria la serie più adatta per risorse fisiche alle esigenze e quindi lo specifico modello. Ovviamente, passando alla fase operativa, sarà necessario considerare la disponibilità di strumenti, come kit e tool di sviluppo sia hardware che software che possano facilitare lo sviluppo dei progetti. In ogni caso conoscere almeno sommariamente l’architettura e le risorse fisiche del controllore è fondamentale. La cosa vale, ovviamente, anche per gli ADuC. Se se ne analizza l’architettura generale (figura 1) appare allora evidente come tra le loro principali caratteristiche vi sia l’integrazione di periferiche analogiche cioè convertitori analogico/digitali (ADC), digitali/analogici (DAC) e comparatori. In questo paragrafo illustreremo, in particolare, le caratteristiche architetturali della sezione di conversione analogico/digitale (ADC). La sezione di conversione ADC del chip ADuC7022, ma anche quella degli altri chip della serie 7000 integra un convertitore ADC multicanale a 12 bit ad alta velocità che può funzionare con tensione di alimentazione compresa tra 2.7 V e 3.6 V e che può lavorare ad una velocità massima di 1 MSPS, velocità raggiungibile con una sorgente di clock pari a 41,78 MHz di ferquenza. L’architettura della sezione ADC multicanale prevede un multiplexer, un T/H (track-and-hold) differenziale, un riferimento di tensione interno e l’ADC. L’ADC è del tipo ad approssimazioni successive (SAR) a 12 bit e può essere configurato per operare in una delle tre seguenti possibili modalità:

- modalità differenziale (adatta all’acquisizione di segnali piccoli e bilanciati);

- modalità Single-Ended adatta all’acquisizione di segnali sbilanciati;

- modalità pseudo-differenziale per segnali single-ended.

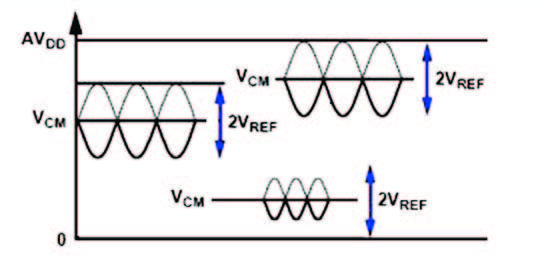

Il converter accetta in ingresso segnali analogici compresi nel range 0-Vref quando l’ADC opera in modalità single-ended o pseudo-differenziale. Nel caso in cui si impieghi invece la modalità differenziale, il segnale deve essere bilanciato intorno alla tensione di modo comune (VCM) in un range compreso tra 0V e AVDD con una escursione massima pari a 2Vref come illustrato schematicamente in figura 8.

Figura 8: schematizzazione di segnali differenziali bilanciati.

Un riferimento ad alta precisione interno a 2.5 V è integrato all’interno del chip, tuttavia è possibile impiegare opportunamente, allo scopo, un riferimento di tensione esterno. E’ possibile eseguire sia conversioni singole che conversione di tipo continuo e come segnale di trigger per l’inizio della conversione è possibile impiegare sia il pin CONVSTART che l’output del PLA integrato on-chip, oppure l’overflow del Timer0 o del Timer1. L’architettura del chip mostra come oltre ai segnali analogici esterni possa essere inviato al MUX anche il segnale proveniente dal sensore di temperature integrato. Questa operazione rende possibile il calcolo della temperatura interna del chip con una precisione pari a ±3ºC.

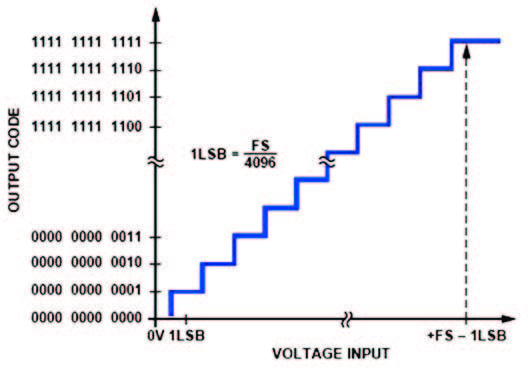

FUNZIONE DI TRASFERIMENTO

Nella modalità di acquisizione pseudodifferenziale ed in quella single-ended il segnale di ingresso è compreso nel range 0V-Vref; il risultato della codifica è di tipo binario senza segno con una risoluzione che può essere calcolata con la seguente relazione (nell’ipotesi che sia Vref = 2.5 V):

1 LSB = FS/4096=2.5 V/4096 =610 V

La scelta di riferire il calcolo alla tensione 2,5V è dovuta al fatto che onchip è disponibile proprio questo valore di tensione di riferimento, pertanto nelle maggior parte dei casi si preferisce sfruttare questo piuttosto che impiegare un riferimento esterno. In figura 9 è riportata la caratteristica di trasferimento dell’ADC per modalità di funzionamento pseudo-differenziale e singleended.

Figura 9: funzione di trasferimento per ADC in modalità pseudo-differenziale e single-ended.

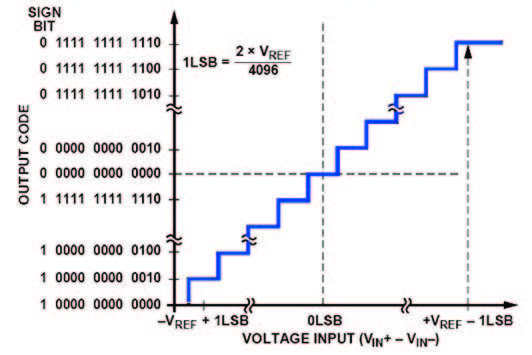

Idealmente la transizione tra una codifica e l’altra è posizionata a metà tra esse e quindi in punti corrispondenti rispettivamente ad 1/2 LSB, 3/2 LSB, 5/2 LSB e così via. Ovviamente, come in tutti gli ADC, questa caratteristica è da considerare ideale poiché non tiene conto di fenomeni reali cui corrispondono errori quali l’errore di non linearità e quello di offset. Nell’acquisizione in modalità differenziale invece, il segnale sottoposto a conversione è quello corrispondente alla differenza dei segnali presenti rispettivamente sui pin Vin+ e Vin-. In questo caso, l’ampiezza massima che il segnale differenziale può raggiungere, consentendo comunque una corretta conversione, è quella compresa tra – Vref e +Vref e corrisponde quindi a 2×Vref. La conversione è eseguita correttamente nonostante il modo comune (CM) il quale analiticamente corrisponde alla media dei due segnali cioè [(VIN+)+(VIN–)]/2, e rappresenta pertanto, fisicamente, il valore intorno al quale sono centrati i due segnali. Il risultato della codifica è in complemento a due con risoluzione pari a:

1 LSB = 2 Vref/4096 =2 × 2.5 V/4096 =

1.22 mV (con Vref = 2.5 V)

La caratteristica ideale di trasferimento in modo differenziale è quella riportata in figura 10.

Figura 10: funzione di trasferimento dell’ADC in modalità differenziale.

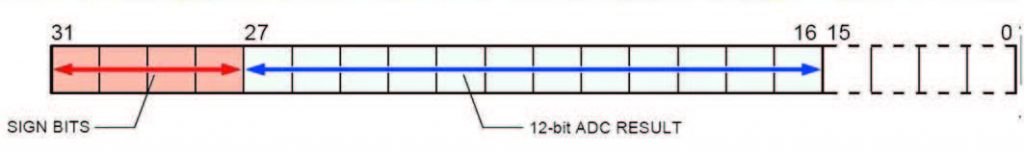

Il risultato della conversione è memorizzato all’interno del registro ADCDAT nel formato schematizzato in figura 11.

Figura 11: registro ADCDAT (Risultato della conversione A/D).

Quest’ultima ma anche le precedenti due figure evidenziano, tra le altre cose, come la conversione sia a 12 bit. In particolare, con riferimento alla figura 11, all’interno del registro ADCDAT troviamo i primi quattro bit destinati ad ospitare il segno; il risultato numerico, a meno del segno, occupa invece l’area compresa tra il bit 16 ed il bit 27 come mostrato nella stessa figura 11. Ovviamente, mentre in modalità differenziale il risultato è rappresentato in complemento a due, in modalità pseudo - differenziale e single - ended il risultato è presentato semplicemente in formato binario senza segno.

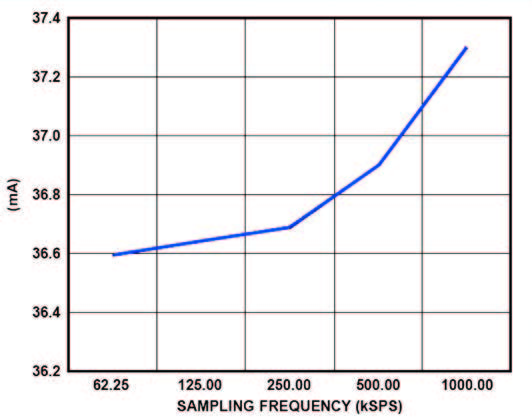

CONSUMO DI CORRENTE DEL CONVERTITORE

L’ADC in standby è alimentato anche se non esegue alcuna conversione. In queste condizioni esso assorbe una corrente pari a 640 µA. L’impiego del riferimento di tensione interna comporta l’aggiunta di altri 140 µA. Durante la conversione a questa corrente è necessario aggiungerne una quantità ulteriore di corrente tanto maggiore quanto maggiore è la frequenza di campionamento. Più precisamente è necessario aggiungere una quantità pari a 0.3 µA moltiplicato per la frequenza di campionamento espressa in kilohertz. La figura 12 mostra l’andamento della corrente assorbita dalla sezione ADC in funzione della frequenza di campionamento.

Figura 12: consumo di corrente dell’ADC in funzione della frequenza di campionamento.

TIMING DELLA CONVERSIONE

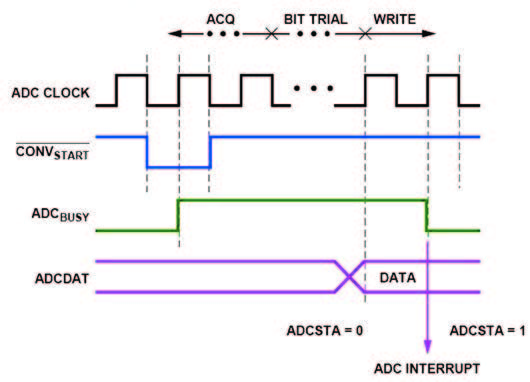

Affinchè la conversione possa avvenire correttamente è necessario che essa sia scandita da un Timing. La figura 13 mostra in dettaglio questo aspetto.

Figura 13: ADC Timing.

Il diagramma di Timing è interpretato nel seguente modo: il pin ADCBUSY indica, se è a valore 1, che la conversione è in corso e pertanto che il risultato della conversione non è ancora stato ottenuto e che non può essere pertanto ancora utilizzato. Il registro ADCSTA indica invece quando la codifica della conversione è disponibile. Il diagramma in particolare fa riferimento al caso in cui sia impieghi il pin CONVSTART come trigger per l’ADC.

REGISTRI DI CONFIGURAZIONE

Anche se vogliamo illustrare solo in modo generale l’hardware del controllore, riteniamo opportuno fornire qualche approfondimento ulteriore specie sui registri che riguardano la funzione A/D visto che questa è una delle funzioni peculiari di questo tipo di controllore. Per la configurazione ed il controllo della sezione A/D occorre gestire i seguenti registri:

# ADCCON: la sua configurazione consente al programmatore di abilitare l’ADC e di impostare modalità operativa ed il tipo di conversione;

# ADCCP: consente di impostare il canale positivo dell’ADC;

# ADCCN: consente di impostare il canale negativo dell’ADC;

# ADCSTA: segnala quando il risultato della conversione è disponibile ed è formato dal solo bit ADCReady che assume valore 1 a conversione avvenuta e torna automaticamente a valore 0 appena il risultato viene letto dal registro ADCDAT che contiene il risultato della conversione;

# ADCDAT: contiene il risultato della conversione (figura 11);

# ADCRST: registro impiegato per effettuare il reset (ritorno ai valori di default) di tutti i registri che riguardano l’ADC;

# ADCGN: calibrazione del guadagno; # ADCOF: calibrazione dell’offset.

ACQUISIZIONE DIFFERENZIALE

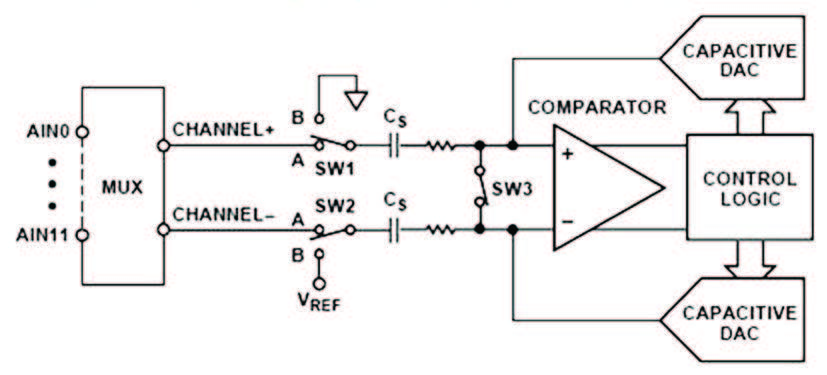

In figura 14 è schematizzata l’acquisizione di tipo differenziale.

Figura 14: acquisizione differenziale e conversione A/D.

L’interruttore SW3 è chiuso mentre SW1 e SW2 sono in posizione A. Il comparatore è allora in uno stato di bilanciamento ed il valore di segnale da convertire è acquisito capacitivamente. Dopo l’acquisizione capacitiva, l’interruttore SW3 passa in posizione OPEN mentre SW1 e SW2 passano in posizione B. Il comparatore viene a trovarsi in una condizione di sbilanciamento ed entrambi gli ingressi appaiono disconnessi dalla sorgente esterna durante tutto l’intervallo di tempo che segue e che porta all’effettiva conversione A/D. La logica di controllo ed i due DAC servono ad aggiungere e sottrarre carica alle capacità di sampling in modo da riportare il circuito nelle condizioni di bilanciamento. Quando si raggiunge nuovamente il bilanciamento la conversione può essere considerata completa e la logica di controllo presenta in uscita la codifica del valore del segnale che era stato campionato. Da un punto di vista elettrico, il campionamento del segnale necessita di impedenza di sorgente identica sui due ingressi (in caso opposto i diversi tempi di assestamento potrebbero comportare errori di conversione).

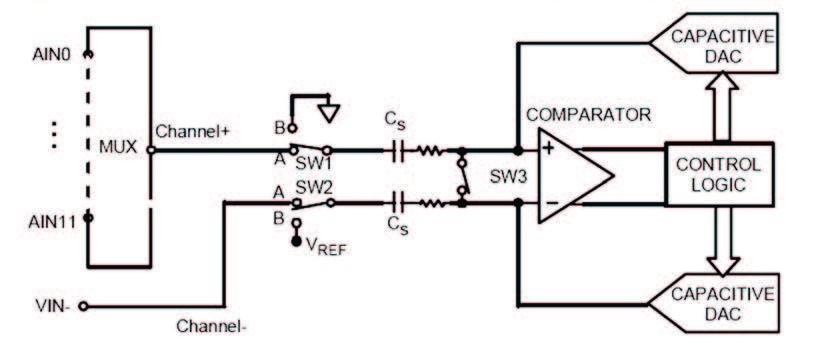

ACQUISIZIONE PSEUDO-DIFFERENZIALE

In modalità pseudo-differenziale (figura 15) vengono ancora una volta utilizzati i pin VIN+ e VIN- così come accade in quella differenziale; SW2 può commutare su Channel- oppure su Vref mentre il segnale di ingresso su VIN- può variare tra VIN- e (VREF+VIN-). Il segnale VINdeve essere tale da non eccedere il valore AVDD.

Figura 15: acquisizione pseudo-differenziale e conversione A/D.

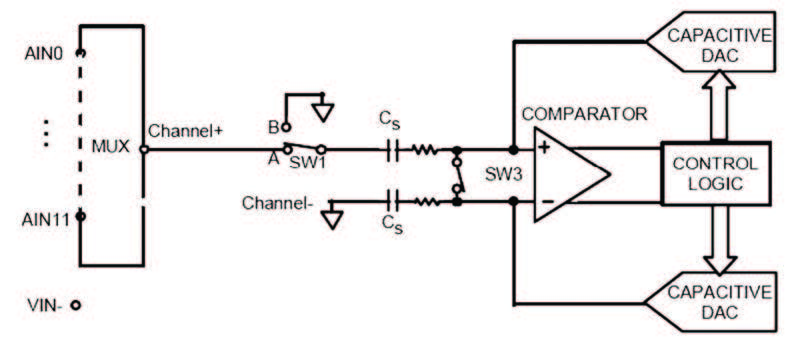

ACQUISIZIONE SINGLE-ENDED

In modalità single-ended (figura 16) SW2 è connesso internamente a massa, VIN- può essere tenuto floating ed il segnale in ingresso deve presentare una dinamica che rientri nel range 0V- Vref.

Figura 16: acquisizione Single-ended e conversione A/D.

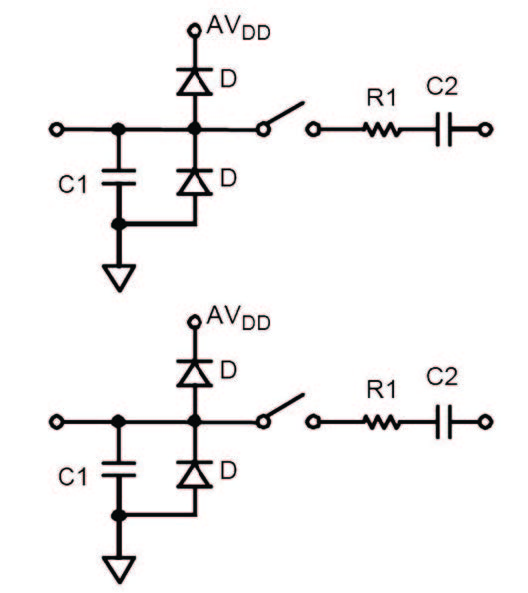

EQUIVALENTE ELETTRICO IN INGRESSO

La figura 17 mostra il circuito equivalente di ingresso dell’ADC. I diodi servono a fornire protezione dalle cariche elettrostatiche.

Figura 17: circuito elettrico equivalente di ingresso dell’ADC.

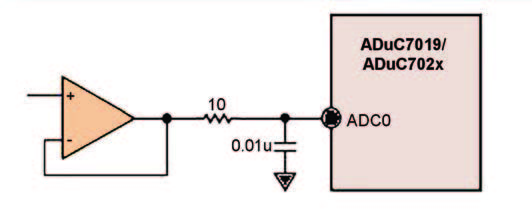

A tal proposito è importante che gli ingressi non superino mai più di 300mV la tensione di alimentazione. I diodi tuttavia non possono sopportare correnti superiori a 10mA, valore oltre il quale rischiano di danneggiarsi irreversibilmente. Mentre C1 (valutabile intorno a 4 pF) può essere attribuita alla capacità del pin, la resistenza, valutabile intorno a 100 ohm, è dovuta allo switch elettronico del circuito di campionamento. La capacità di sampling C2 è invece voluta in quanto necessaria per all’operazione di campionamento e presenta valori intorno a 16 pF. Poiché una delle applicazioni principali dei chip ADuC è quella di acquisizione di segnali analogici per applicazioni A/D è necessario porre particolare attenzione al modo in cui il segnale da acquisire è interfacciato non solo internamente al chip ma anche esternamente. Per applicazioni AC può essere allora opportuno rimuovere componenti ad alta frequenza dal segnale analogico in ingresso mediante l’impiego di un filtro bassa-basso RC. Occorre inoltre valutare di volta in volta l’eventuale necessità di interfacciare la sorgente di segnale con il pin di ingresso del chip attraverso uno stadio buffer. Per esempio, in applicazioni in cui la distorsione (THD-Total Harmonic Distortion) oppure il rapporto segnale rumore (SNR-Signal to Noise Ratio) sono aspetti critici è opportuno che l’impedenza di uscita della sorgente sia bassa. Se questa condizione non è rispettata è possibile impiegare un circuito di interfacciamento come quello di figura 18 in cui si introduce un buffer con impedenza di ingresso teoricamente infinita tra la sorgente ed il pin fisico di acquisizione del controller.

Figura 18: buffering del segnale in ingresso (modalità single-ended o pseudodifferenziale).

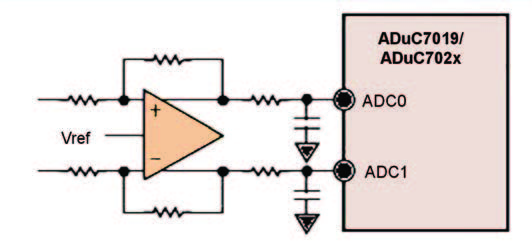

Il circuito fa riferimento ad un ingresso del chip ADuC impiegato in modalità Single-ended o pseudo differenziale. In figura 19 è invece riportato l’analogo circuito di interfacciamento per segnali che necessitano di acquisizione differenziale.

Figura 19: buffering del segnale in ingresso (modalità differenziale).

Quando nessun amplificatore è impiegato come interfaccia tra la sorgente ed il pin di ingresso del chip, l’impedenza della sorgente dovrebbe essere limitata al di sotto di 1 kΩ, in tutti gli altri casi è opportuno impiegare lo stadio buffer tanto più quanto più alta è l’impedenza della sorgente.

IL SENSORE DI TEMPERATURA INTEGRATO

Gli ADuC7019 / 20 / 21 / 22 / 24 / 25 / 26 27 / 28 / 29 integrano un sensore di temperature on chip che fornisce un segnale (in tensione) in uscita proporzionale alla temperatura. Il segnale di tensione così ottenuto generato internamente può essere interfacciato con il multiplexer dell’ADC per monitorare la temperatura interna del chip con una accuratezza di ±3°C.

RIFERIMENTO DI TENSIONE A BAND GAP

Il microcontrollore ADuC7022, come tutti gli altri della serie 7000 è dotato di un riferimento di tensione a band gap integrato on-chip (2,5V) che può essere utilizzato per il funzionamento delle conversioni A/D. Lo stesso valore di tensione, fornito dal riferimento a band gap, è reso disponibile sul pin Vref in uscita. L’impiego di questo riferimento interno prevede l’impiego di una capacità pari a 0.47 F connessa esternamente tra lo stesso pin Vref ed AGND. Tale componente aiuta a rendere stabile il riferimento e veloce la risposta dell’ADC durante le conversioni. Il fatto di rendere disponibile la stessa tensione di riferimento sul pin Vref consente di sfruttare questa sorgente come riferimento per altri circuiti. In questo caso, tuttavia, può essere opportuno interporre tra il riferimento Vref ed il circuito esterno un buffer che consenta di compensare la bassa corrente che il pin Vref può fornire in uscita. Attraverso l’impostazione di un apposito registro (REFCON) è possibile abilitare il riferimento interno per le conversioni A/D o disabilitarlo oppure abilitare il passaggio della stessa tensione di riferimento Vref sul pin di uscita Vref.

DAC

Quasi tutti I modelli della serie 7000 degli ADuC integrano, a seconda del particolare modello, un certo numero di DAC a 12-bit. Ogni DAC è configurabile indipendentemente dagli altri attraverso opportuni registri. Fa eccezione proprio il modello ADuC7022 che non integra questa risorsa hardware. Per questo motivo evitiamo di dilungarci sull’argomento. Tuttavia, chi voglia approfondirlo per gli altri modelli della serie ADuC7000 può far diretto riferimento ai documenti riportati nella sezione “Riferimenti bibliografici” liberamente scaricabili dalla rete.

LA FUNZIONALITÀ “POWER SUPPLY MONITOR”

I chip della serie 7000 integrano onchip il monitoraggio della tensione di alimentazione sul pin IOVdd. A questa funzionalità è destinato il registro PSMCON. L’integrazione di questa funzionalità aiuta il chip ad evitare perdita di dati a causa di un abbassamento di tensione di alimentazione, poiché in questo caso lo stato dei registri viene salvato e l’esecuzione del codice riprende solo se è ristabilito il corretto livello di alimentazione.

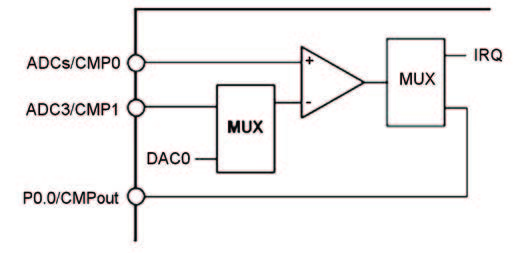

IL COMPARATORE

L’ADuC 7022, come gli altri della serie 7000, integra un comparatore di tensione. L’ingresso positivo del comparatore è multiplexato con l’ingresso ADC2 mentre quello negativo è multiplexato con ADC3 come è possibile osservare sul pin-out del chip (figura 3). Diversamente da quanto accade negli altri chip della serie 7000, nell’ADuC7022 (e negli ADuC7025 e ADu7027) non è possibile indirizzare il segnale DAC0 sull’interfaccia di ingresso corrispondente ad ADC3. Questo toglie qualche funzionalità al chip rispetto ad altri della stessa serie in quanto non consente di riutilizzare un segnale convertito in analogico per l’operazione di comparazione. Questo aspetto deriva direttamente da un scelta architetturale che non prevede l’integrazione di DAC all’interno del modello ADuC7022. Nel caso in cui sia necessario disporre di questa funzionalità è necessario puntare sull’impiego di un altro modello di ADuC della stessa serie 7000. In questo caso l’architettura del comparatore è schematizzabile come in figura 20.

Figura 20: schematizzazione dell’architettura del comparatore negli ADuC della seroe 7000 ad eccezione dei modelli 7022, 7025 e 7027.

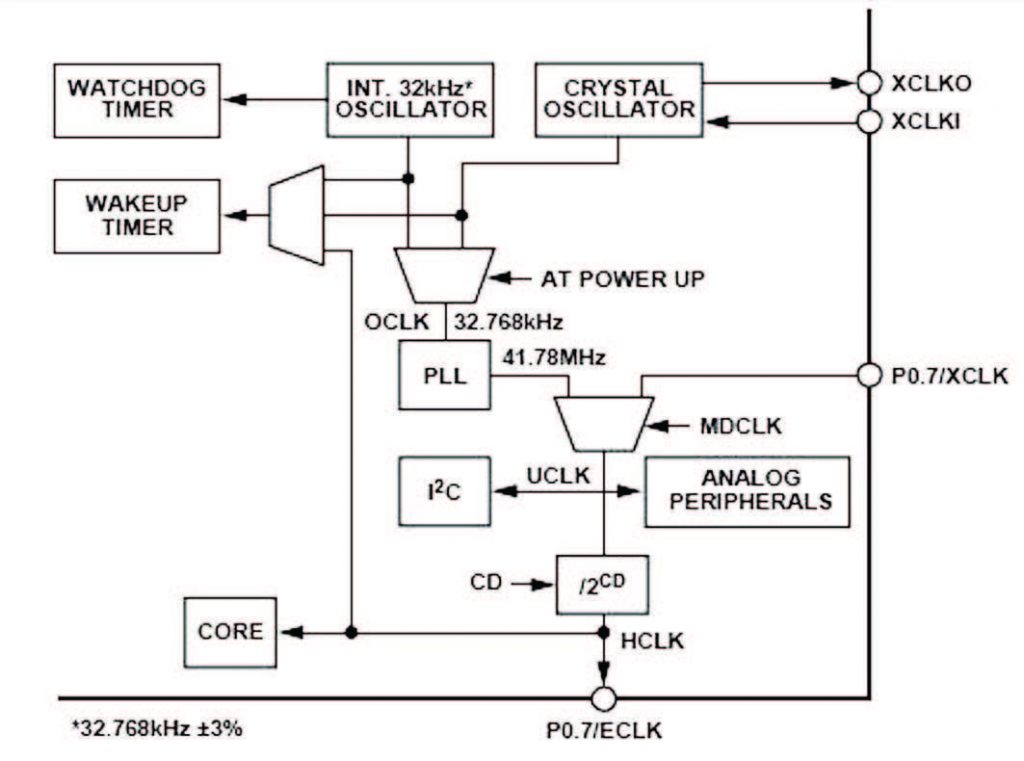

IL CLOCK

Gli ADuC della serie 7000 integrano un oscillatore a 32.768 kHz ±3%, un divisore di clock ed un PLL. Attraverso un moltiplicatore (fattore 1275) il clock interno o eventualmente un clock esterno alla stessa frequenza (32.768 kHz) può essere impiegato per ottenere un clock di sistema pari a 41.78 MHz (UCLK). Il core può operare direttamente a questa frequenza oppure ad una frequenza sottomultipla binaria. Il clock per il funzionamento del core può anche essere fornito all’esterno (pin ECLK), tuttavia in questo caso non è opportuno impiegare tale segnale per pilotare direttamente un dispositivo esterno (è preferibile impiegare un adeguato stradio buffer interposto tra i due chip). La figura 21 schematizza in maniera sintetica quanto esposto.

Figura 21: il circuito di clock.

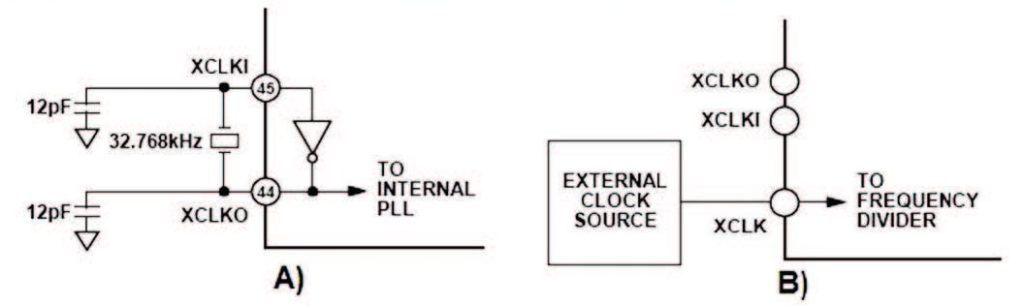

La sorgente di clock può essere generate mediante il PLL interno o essere affidato ad una sorgente esterna. Nel primo caso è necessario collegare un quarzo a 32.768 kHz tra i pin XCLKI e XCLKO, e connettere due capacità come mostrato in figura 22-a.

Figura 22a: clock generato internamente mediante Oscillatore esterno; B)Clock esterno.

Il cristallo aiuta il PLL a generare con precisione la frequenza pari a 41.78 MHz. Se diversamente non si impiega il quarzo l’oscillatore interno fornisce una frequenza di clock pari a 41.78 MHz ± 3%. Se si impiega invece una sorgente di clock esterna è necessario impiegare il pin P0.7 XCLK (figura 22-b) e configurare opportunamente il Bit 1 ed il Bit 0 del registro PLLCON.

PIN DI INPUT/OUTPUT GENERAL-PURPOSE

Gli ADuC della serie 7000 dispongono di una serie di pin bidirezionali general-purpose (GPIO pin) in numero maggiore o minore a seconda del particolare modello. Tutti i pin possono sopportare una tensione massima in ingresso pari a 5V. In generale si tratta di pin che multiplexano diverse funzioni (figura 3). Tutti i pin GPIO presentano una resistenza interna di pull-up di circa 100 kÙ e possono erogare una corrente massima pari a 1.6 mA. Un limite è imposto tuttavia al numero massimo di pin GPIO che possono contemporaneamente fornire in uscita la corrente massima di 1,6 mA, fissato a Configurando opportunamente il registro GPxPAR è possible disabilitare/abilitare il resistore di pull-up per le porte P0 e P1. Infatti, nella serie 7000 i pin GPIO sono in raggruppati in cinque porte da port 0 a Port 4. Nel caso specifico del modello 7022 che presenta un minor numero di pin rispetto agli altri modelli della serie sono disponibili le sole port0 e port1.

GLI INTERRUPT

Anche i controllori ADuC, come qualunque processore, sono dotati di interrupt in grado di modificare il flusso del programma in occasione di determinati eventi interni o esterni. I controllori della serie 7000 presentano 23 interrupt complessivi di tipo IRQ (Normal Interrupt Request) o FIQ (Fast Interrupt Request) come è tipico del core ARM7TDMI. La maggior parte degli interrupt riguardano le periferiche integrate sul chip come i convertitori ADC, i Timer, la I2C e la UART. Quattro ulteriori interrupt possono essere generati esternamente sui pin IRQ0, IRQ1, IRQ2, and IRQ3.

PORTE DI COMUNICAZIONE

Qualunque processore ha la necessità di comunicare con periferiche e dispositivi esterni. Questo può avvenire mediante diversi tipi di interfaccia. Gli ADuC della serie 7000 sono tipicamente dotati di:

- UART

- SPI

- I2C

- porte di I/O General purpose.

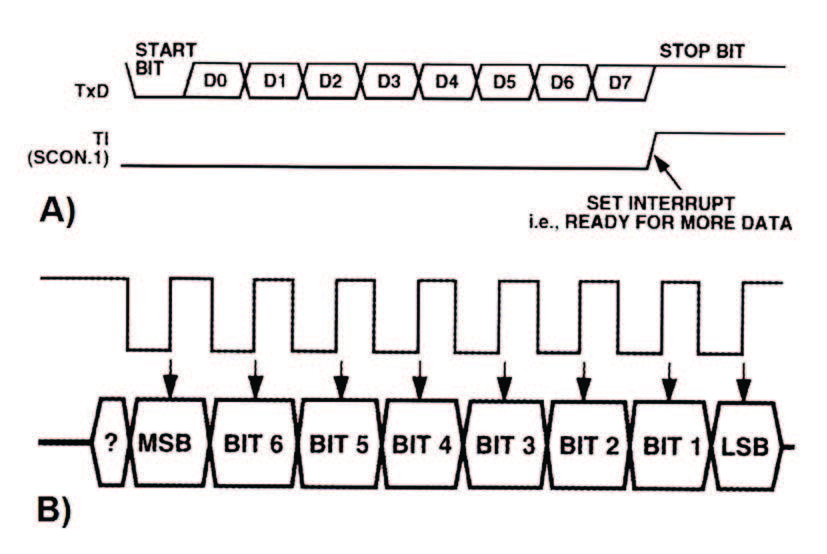

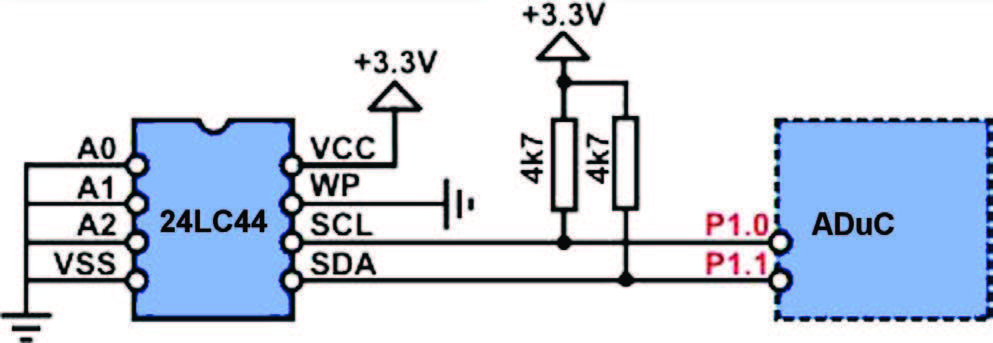

Il chip dispone infatti di un porta seriale che può essere configurata in diversi modi. Essa multiplexa diverse periferiche (SPI, UART, e due I2C). I pin interessati possono pertanto essere configurati in modo da ricoprire una determinata funzione piuttosto che un’altra. La periferica UART è una porta di comunicazione tipicamente full-duplex che consente trasmissione e ricezione asincrona cioè comunicazione bidirezionale. Essa prevede, infatti, una linea di trasmissione (TX) e duna linea di ricezione (RX) che si interfaccia ad un buffer. La comunicazione, essendo di tipo asincrono, non prevede l’impiego di un clock, motivo per cui ciascun byte è fatto precedere da un bit di start ed è fatto seguire da un bit di stop (figura 23-a). L’interfaccia SPI (Serial Peripheral Interface) è invece uno standard industriale seriale sincrono full duplex. Essa può essere configurata come master o slave ed impiega tipicamente quattro pin: MISO (Master In, Slave Out), MOSI (Master Out, Slave In), SCL (Serial Clock I/O) e CS Chip Select. Lato trasmissione il registro SPITX carica il dato sul pin di trasmissione (in slave mode, MISO; in master mode, MOSI); il bit di stato della trasmissione (Bit 0 in SPISTA) indica quando è presente un dato valido nel registro SPITX. Analogamente, in ricezione, funzionano il registro SPIRX ed il bit 3 di SPISTA. Il fatto che si tratti di una comunicazione sincrona, così come avviene per la porta I2C, è una delle principali differenze rispetto alla porta UART. E’ presente infatti un clock che scandisce la trasmissione. In pratica si tratta delle interfacce tipicamente impiegata per la comunicazione con memorie flash esterne o SIM card o memorie EEPROM (figura 24). In questo caso la velocità di trasmissione dipende dal clock che scandisce la trasmissione stessa. In figura 23b è schematizzata una trasmissione seriale sincrona. Ovviamente la disponibilità sui microcontrollori delle interfacce di comunicazione sincrone ed asincrone è motivata soprattutto dall’indubbio vantaggio di necessitare di poche linee fisiche per la comunicazione, sebbene questo approccio comporti limiti sulla velocità massima di trasmissione.

Figura 23b: schematizzazione di una trasmissione seriale asincrona (si noti il bit di start e quello di stop); B)Schematizzazione di una trasmissione seriale sincrona (si noti il segnale di clock).

Figura 24: esempio di comunicazione tra una memoria EEPROM (24LC64) ed un ADuC su bus I2C.

PROGRAMMAZIONE E SICUREZZA

I 62 kB di memoria Flash/EE possono essere programmati in-circuit, mediante un download seriale (standard UART) o attraverso il protocollo JTAG che consente il download ed il debug del codice. Essi possono inoltre essere protetti da lettura e scrittura (registro FEEPRO/FEEHIDE MMR). Il registro suddetto può essere protetto da una chiave che ne impedisce l’accesso diretto. Per modificare il contenuto del registro è necessario impiegare nuovamente la chiave. Il chip diversamente può essere sbloccato operando una cancellazione globale ma questo, come è ovvio aspettarsi, cancella completamente il contenuto della memoria flash e quindi il codice memorizzato sul controllore. E’ anche prevista la possibilità di impiegare il registro di configurazione di sicurezza per una protezione permanente. Quest’ultima è attivata impiegando un particolare valore di chiave. In questo caso, tuttavia, non è più possibile modificare nuovamente il contenuto di tale registro e pertanto non è possibile rimuovere la protezione e di conseguenza non è più possibile sbloccare la memoria flash a meno che non si esegue una cancellazione completa del chip, cosa che comporta la perdita stessa del codice.

ALCUNE CONSIDERAZIONI SULL’ALIMENTAZIONE

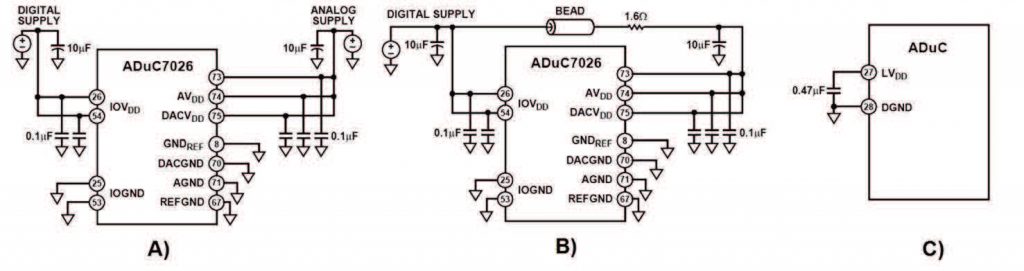

Gli ADuC della serie 7000 prevedono alimentazione compresa nel range 2.7V-3.6 V. I chip prevedono alimentazione separate per pin analogici e digitali (AVDD e IOVDD) in modo da limitare problemi derivanti da rumore causato dalla variazione di livelli digitali. Questo approccio consente, senza alcun problema, di utilizzare anche tensioni di valore differenti, come mostrato nella schematizzazione di figura 25a per le due sezioni (per esempio 3,3V per la parte digitale e 3V per la parte analogica o viceversa). Nel caso in cui non si disponga di due alimentazioni separate è possibile ridurre l’effetto del rumore sulla parte analogica (AVDD) impiegando un resistore ed una ferrite opportunamente dimensionate interposte tra AVDD ed IOVDD, come mostrato in figura 25B.

Figura 25a: alimentazioni separate; B) Alimentazione unica; C) Filtro sull’alimentazione IOVDD.

APPROCCIO ALLA PROGETTAZIONE E CONCLUSIONI

Development Tools low cost sono disponibili per molti controllori ADuC e anche per quelli della famiglia ADuC702X. Si tratta di tool facilmente installabili in ambiente Windows che prevedono, tipicamente, una ADuC702X Evaluation board dotata di porta di programmazione seriale e relativo cavo, software e debugger in circuit (JTAG-based). Ovviamente, per quanto concerne gli aspetti di programmazione sarà necessario fare diretto riferimento al manuale dello specifico modello di controllare utilizzato, in modo da avere un riferimento specifico sulle risorse fisiche (memoria, registri, interrupt, ADC, DAC, Timer) di cui si dispone prima ancora di passare allo sviluppo e alla programmazione vera e propria.