Lo sviluppo di applicazioni basate su trasmissione di dati attraverso reti LAN o WAN ha portato alla necessità di una sempre maggiore protezione delle informazioni trasferite. Il processore Moschip MCS1000, si presenta con un valido supporto per progetti in cui la sicurezza è uno degli aspetti fondamentali.

Introduzione

Il security processor MCS1000 di Moschip si propone come la soluzione ideale per lo sviluppo di progetti basati su comunicazione Ethernet, in cui la sicurezza dei dati trasmessi è il punto centrale dell’intero progetto. Si tratta di un system-on-chip (SOC) dalle elevate prestazioni, che permette di implementare una VPN (Virtual Private Network) basata sul protocollo di criptaggio/autenticazione IPSec, grazie al relativo hardware on-board. L’articolo vuole dare una visione d’insieme del processore ed in particolare della sua architettura interna, delle schede di valutazione e dei sistemi operativi che esso supporta. L’MCS1000 è costituito da tre gruppi funzionali:

- Il sottosistema CPU.

- Il modulo hardware IPSec.

- Il blocco delle interfacce generali.

Il sottosistema CPU contiene un core ARM926EJ-S a 200MHz, con una architettura RISC 32-bit. Esso sovrintende a tutte le funzioni di gestione del MCS1000 e risulta ben integrato con il modulo hardware di crittografia. Quest’ultimo ha il compito di gestire tutte le funzioni relative al protocollo IPSec, riducendo il carico di lavoro destinato alla CPU. In particolare, esso implementa gli algoritmi DES, 3DES, AES, MD5 e SHA. Infine il blocco delle interfacce è formato da:

- Controller della memoria.

- Controller del bus PCI.

- Interfaccia Ethernet.

- Linee I/O general purpouse.

- PLL (Phase Lock-Loop).

- Registri di bootstrap.

Il controller della memoria può interfacciarsi sia a dispositivi SDRAM che Flash. Il controller SDRAM supporta fino a 64MB, mentre quello della Flash dispone di 26 linee di indirizzo per un totale di 256MB di memorizzazione non volatile. L’interfaccia PCI è a 32-bit, con una frequenza del bus a 33MHz e risulta compatibile con lo standard PCI 2.0. Il controller integrato agisce come disposto slave. Esso non può fungere però da dispositivo host in quando non è dotato di un arbitraggio del bus PCI. L’MCS1000 è dotato di tre controller Ethernet 10/100, ognuno dei quali è costituito da un MAC (Media Access Controller) ed un PHY (Physical Layer) indipendenti. Tale interfaccia può essere connessa direttamente ai connettori di rete (RJ45), senza inserimento di componenti esterni. Le interfacce di I/O sono costituite da 16 GPIO (General Purpouse I/O), una UART ad alta velocità (115200 baud) e una JTAG, utilizzata esclusivamente per test e debug. Le linee general purpouse sono controllate direttamente dal core del processore e possono essere utilizzate per operazioni su bit o di controllo. Il sistema PLL permette la generazione dei diversi clock necessari per i vari blocchi digitali. Infine i registri di boostrap permettono di impostare quattro fondamentali caratteristiche di funzionamento dell’MCS1000: modalità di debug, velocità del processore, disabilitazione ROM interna e funzioni definite dall’utente. Il chip MCS1000 supporta ogni sistema operativo previsto per la piattaforma ARM926EJ-S, tra cui Windows-CE, VxWorks e Linux.

L’altro punto di forza di questi processori è disponibilità di varie schede di valutazione per testare il funzionamento del chip sia in modalità Stand-Alone che in modalità Periferica (i due concetti saranno chiariti successivamente). Le EVB si distinguono tra quelle che permettono di testare la funzionalità VPN e quelle che implementano un NIC (Network Interface Controller):

- MCS1000-EVB-6port VPN

- MCS1000-EVB-3 Port VPN

- MCS1000-EVB-3 Port NIC

- MCS1000-EVB-1 Port NIC

Architettura interna

Si cercherà ora, dopo questo sguardo d’insieme del processore, di entrare nel dettaglio della architettura per comprendere come sono organizzati tra loro i vari blocchi e come sfruttare le elevate potenzialità di cui è dotato.

Modalità di esecuzione

L’MCS1000 ha due modi di esecuzione:

- Stand-Alone.

- Peripheral.

Nella prima modalità il processore opera autonomamente e non richiede un host che funga da supervisore. Il core ARM esegue il prelievo delle istruzioni direttamente dalla Flash esterna. In tale condizione il bus PCI risulta inattivo. Le applicazioni che ben si prestano a questa configurazione sono VPN/Firewall di basso costo. Nella modalità periferica, invece, l’MCS1000 funziona da FEC (Fast Ethernet Controller) sicuro. Esso agisce come un dispositivo presente sul bus PCI. Applicazioni tipiche sono realizzazione di schede di rete o router.

Descrizione dei bus interni

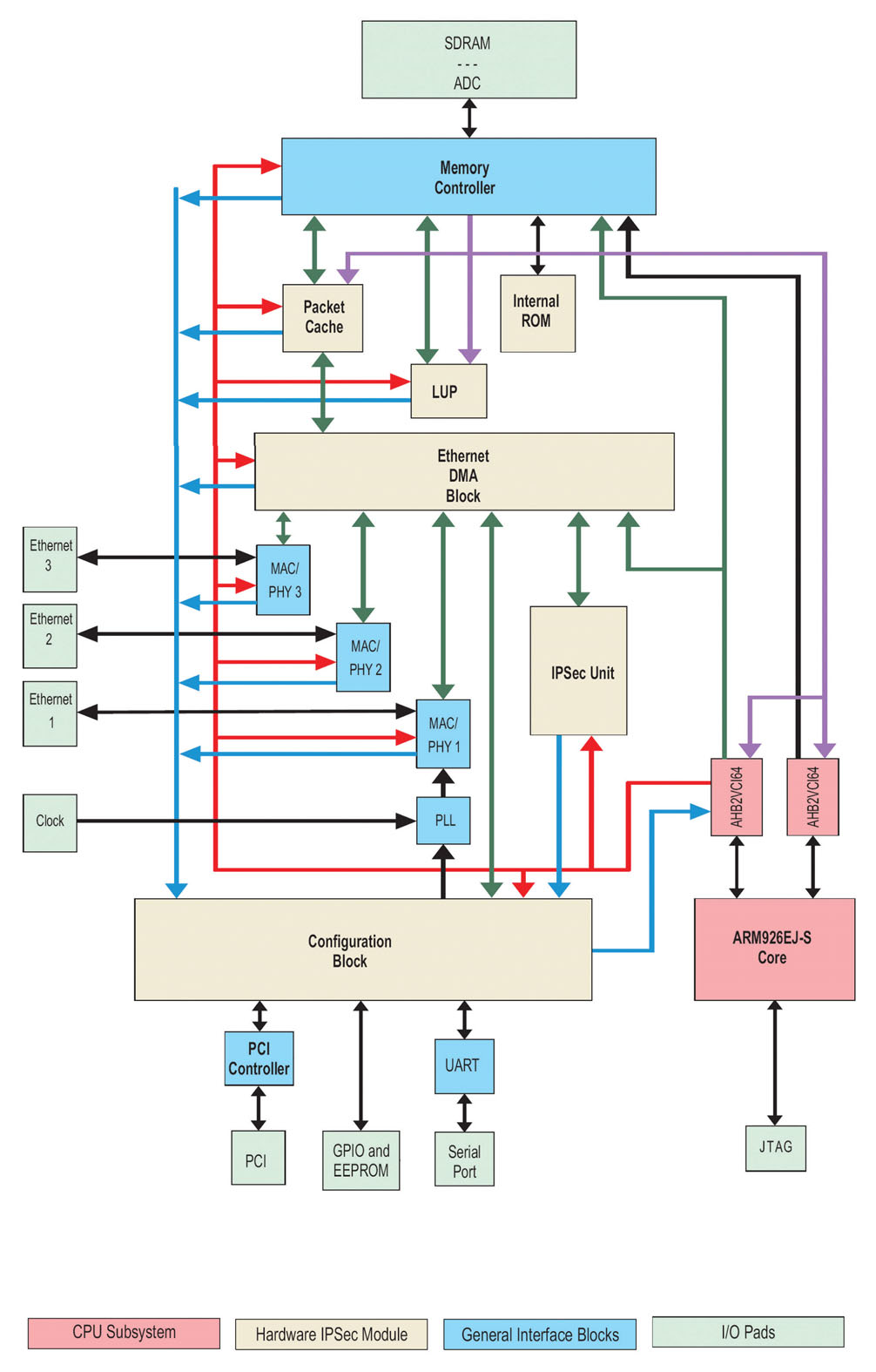

Lo schema a blocchi completo del dispositivo della Moschip è riportato in Figura 1; ad esso si farà riferimento nel corso dell’articolo. In particolare, sono stati evidenziati in rosa i blocchi che si riferiscono al sottosistema della CPU, in grigio quelli relativi al modulo IPSec, in azzurro i blocchi di interfaccia ed infine in verde i pad di I/O che rappresenta la frontiera con il “mondo esterno”. In Figura 1 si può notare che anche le linee dei bus (come i blocchi) hanno un differente colore a seconda della loro funzione.

Il bus rosso permette al sottosistema CPU di indirizzare le varie periferiche. Il bus indicato con il colore blu consente alle periferiche di inviare dati alla CPU, passando attraverso il blocco di configurazione. I bus rappresentati in verde e in viola servono per lo scambio dati. Infine il bus in nero viene utilizzato per l’indirizzamento della memoria esterna, attraverso il Memory Controller. Tutti i bus dati sono a 64-bit con una frequenza operativa di 50MHz. I blocchi che si trovano all’interno dell’unità IPSec (crittografia, autenticazione e I/O) trasferiscono ad una frequenza pari a 50MHz, eccetto i quattro blocchi di crittografia che lavorano ad una velocità di bus pari a 100MHz. Il blocco PLL è in realtà costituito da 2 sottoblocchi. Il primo di questi è dedicato alla CPU e l’altro è per il modulo IPSec ed i restanti blocchi. Entrambi i clock prendono il segnale a 25MHz dal clock dei blocchi PHY.

Il sottosistema CPU

Il security processor MCS1000 si avvale del core ARM926EJ-S prodotto da ARM. Ulteriori informazioni su questo processore possono essere reperite sul sito del produttore, all’indirizzo http://www.arm.com/. È importante evidenziare che esistono alcune differenze tra il modello 926 implementato nel MCS1000 e quello standard (ARM926EJ-S). In aggiunta all’ARM9, infatti, il sottosistema CPU include un bus di interfaccia da ARM9 AMBA (AHB, utilizzato da ARM) a VCI (Virtual Component Interface). Essa è necessaria per connettere il core al modulo IPSec per l’implementazione del protocollo di sicurezza. L’MCS1000 include tutte le funzioni del modello standard eccetto quella per la porta ETM (Embedded Trace Macrocell). Di seguito sono elencate le principali caratteristiche del modello ARM926EJ-S, che si ritrovano invariate anche sull’MCS1000:

- Unità di gestione della memoria (MMU)

- Cache: il core dispone di una cache di 32KB per le istruzioni e 32KB per idati.

- Interfaccia JTAG: la caratteristica EXTEST propria dell’interfaccia JTAG non è implementata sul modulo Moschip.

Il modulo IPSec

Tale modulo permette di aumentare notevolmente le performance dell’MCS1000, in quanto accelera le operazioni del protocollo IPSec ed in particolare quelle relative ad ESP (Encapsulating Security Payload) e AH (Authentication Header). Gli algoritmi di criptaggio e autenticazione che sono stati implementati sono i più diffusi (DES, 3DES, AES, SHA-1, SHA-256 e MD5). Bisogna evidenziare che l’algoritmo AES può essere eseguito nelle sue varianti a 128/192/256 bit. I blocchi costitutivi del modulo IPSec sono di seguito elencati e descritti brevemente (per ulteriori approfondimenti si può far riferimento all’articolo “Il modulo VPNow del microcontrollore MCS1000” pubblicato sul numero di maggio di Firmware):

- Blocco di configurazione: contiene tutti i registri di configurazione, oltre alle varie interfacce di gestione.

- Blocco Ethernet DMA: costituisce l’insieme dei canali di accesso diretto alla memoria per MAC, PCI e modulo di cifratura.

- Look Up Accelerator (LUP): permette di alleggerire il carico della CPU.

- Packet cache: è la cache interna utilizzata per i pacchetti ethernet. Questo permette di incrementare le prestazioni dell’intero sistema poiché i pacchetti non devono essere memorizzati nella RAM esterna.

- RNG (Random Number Generator): serve per la generazione di numeri casuali. Utilizzato soprattutto per l’implementazione della tecnica CSMA-CD per la rilevazione delle collisioni. Infatti, se il dispositivo che deve trasmettere rileva una collisione, allora interrompe la trasmissione attendendo un tempo casuale prima di ritrasmettere.

- Unità IPSec: contiene i blocchi di I/O, i canali DMA e i blocchi Operator. Questiultimi contengono i blocchi di criptaggio (DES, 3DES, AES) e quelli di autenticazione (MD5, SHA-1 e SHA-256). I primi sono anche indicati con il termine di blocchi BL, mentre i secondi come blocchi HM. La Tabella 1 riporta le principali caratteristiche riferite ai succitati algoritmi.

Interfacce Ethernet

L’MCS1000 dispone di ben tre 3 FEC (Fast Ethernet Controller). Essi implementano il layer fisico e MAC. Le linee del controller PHY possono essere collegate direttamente ad un connettore RJ-45, dotato di trasformatori di filtro e disaccoppiamento. L’utilizzo del DMA in abbinamento con tali interfacce è stata una soluzione decisiva sulle prestazione del sistema. Infatti, i trasferimenti verso la memoria vengono automatizzati e non è necessario che intervenga la CPU, la quale può svolgere, intanto, altri compiti. Il blocco TLI (Transaction Layer Interface) è un bus a 32-bit, progettato appositamente per interfacciare il controller DMA con il MAC. Esso è dotato di un buffer di ricezione/trasmissione di 2KB. Le principali caratteristiche del modulo MAC sono elencate di seguito:

- Compatibilità alle specifiche 802.3/802.3u.

- Supporto per trasferimento a 10/100Mbps.

- Supporto VLAN.

- Supporto full-duplex/half-duplex.

- Rilevamento delle collisioni e auto ritrasmissione in modalità half-duplex (per implementare la tecnica CSMA-CD).

- Generazione del preambolo.

- Generazione/verifica CRC.

- Modalità flessibile per il filtraggio degli indirizzi.

Le caratteristiche più rilevanti del modulo PHY, invece, sono di seguito elencate:

- Affidabilità dei dati su cavi di lunghezza fino a 100m.

- Supporto per trasformatori aventi rapporto di trasformazione 1.41:1 (ad esempio Tyco 1605011-1).

- Funzionalità di wave-shaping; questo rende non necessari filtri esterni.

- Indicazioni a LED (3 per ogni porta), configurabili per le seguenti funzioni link, attività in trasmissione/ricezione, collisione, velocità 10Mbps, velocità 100Mbps, full/half duplex.

- Modalità di test e loopback interno.

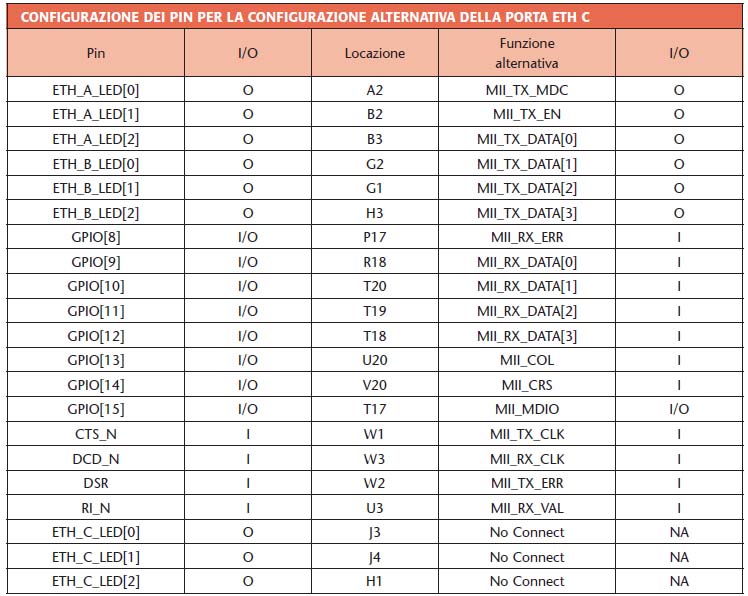

Esistono due configurazioni per il PHY. Quella standard porta le tre interfacce Ethernet sui pin del processore. In alternativa è possibile impostare solo due PHY verso l’esterno e sfruttare in questo modo i relativi pin che risultano liberi (solo sulla porta ETH C può essere impostata questa modalità). La Tabella 2 elenca la funzione dei pin nella configurazione alternativa (per maggiori dettagli sulla funzionalità di tali pin si rimanda al datasheet scaricabili all’indirizzo http://www.moschip.com).

Interfaccia EEPROM seriale

Tale interfaccia può essere usata per comunicare con qualsiasi dispositivo SPI. Fondamentalmente però è sfruttata per interfacciare l’MCS1000 con una EEPROM, necessaria per conservare i tre indirizzi MAC dei relativi controller. Oltre a ciò ovviamente possono essere memorizzate altre informazioni.

Porta seriale

La porta seriale è usata come un UART standard ed è dotata oltre che dei pin TX ed RX anche di quelli per il controllo del flusso (RTS, CTS, DSR, DTR, DCD) e per la segnalazione della ring nel caso di modem (RI). I livelli di uscita sono quelli standard ed è richiesto un traslatore di livello RS-232 nel caso si desideri comunicare con un PC. La velocità di trasferimento può variare da 1200baud a 115.2Kbaud.

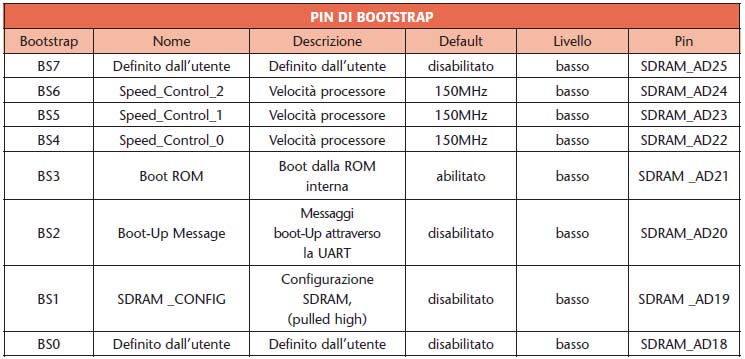

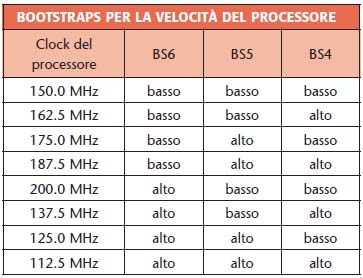

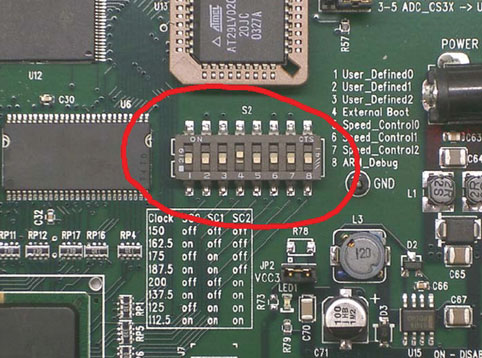

Bootstraps

Ci sono alcuni attributi dell’MCS1000 che è necessario impostare mediante appositi registri detti di bootstrap. Essi controllano quattro aspetti: modalità debug, velocità processore, disattivazione ROM interna e altre impostazioni definite dall’utente. In Tabella 3 sono riportati tutti i pin di bootstrap, mentre in Tabella 4 vengono mostrati i registri su cui bisogna agire se si vuole modificare la velocità del processore.

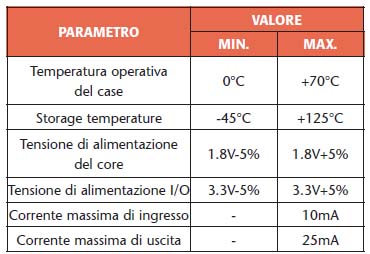

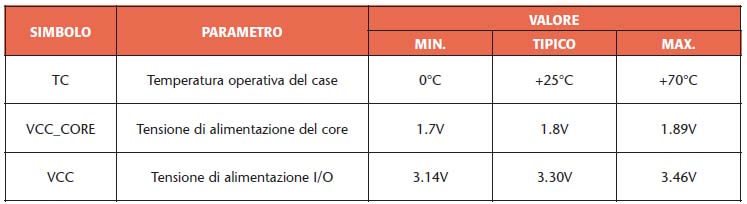

Caratteristiche elettriche e meccaniche

Condizioni operative

In Tabella 5 sono riportate le caratteristiche di funzionamento massime. Oltre questi valori non è più garantito il normale funzionamento e c’è il rischio di un danneggiamento permanente.

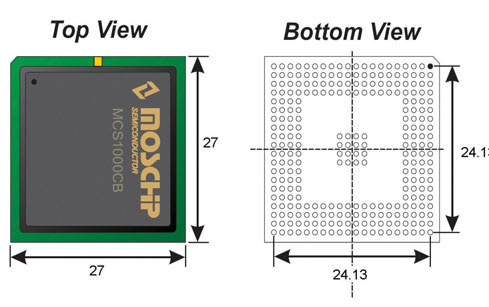

Package

Il chip MCS1000 viene montato in un package del tipo PBGA (Plastic Ball Grid Array) con 272 pin. Le viste top e bottom del package sono riportate in Figura 2.

Come si può osservare l’occupazione di questo chip è di appena 0.73cm2. L’uso di un package PBGA è una scelta necessaria quando, come in questo caso, le frequenze di clock raggiungono valori elevati. In questo modo si riesce a ridurre la lunghezza dei pin, riducendo conseguentemente l’effetto induttivo che questi hanno ad elevate frequenze.

Schede di valutazione

Le schede di valutazione che la Moschip mette a disposizione degli sviluppatori per progetti basati su MCS1000 sono le seguenti:

- MCS1000-EVB-6port VPN

- MCS1000-EVB-3 Port VPN

- MCS1000-EVB-3 Port NIC

- MCS1000-EVB-1 Port NIC

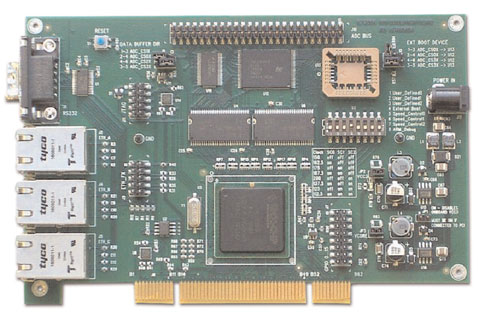

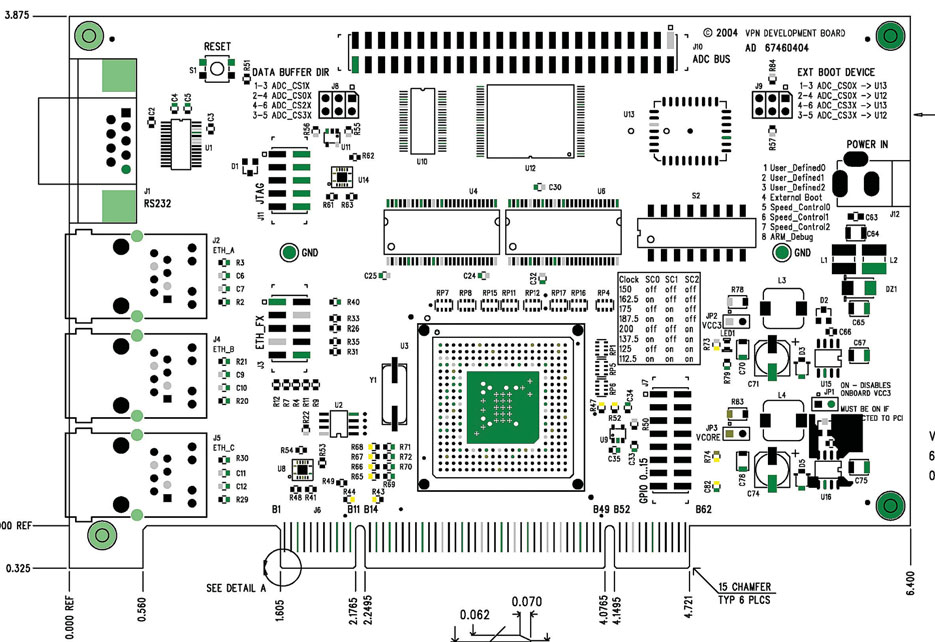

In particolare, si analizzeranno le caratteristiche della MCS1000-EVB-3 Port NIC, la quale può essere inserita nello slot PCI di un PC ed utilizzata sia in modalità stand-alone che periferica. La Figura 3 mostra l’immagine di tale supporto, mentre la Figura 4 riporta uno schema della disposizione dei componenti.

È interessante notare che Moschip fornisce gli schematici di tale scheda; questo può risultare molto utile per chi volesse realizzare un board personalizzata. Tali informazioni sono reperibili sul manuale della scheda di valutazione. In modalità stand-alone, la scheda può avviare il S.O. Linux (precaricato) e funzionare autonomamente senza essere inserita nello slot PCI. Nella modalità periferica, deve invece essere inserita nello slot PCI e permette di realizzare una scheda di rete sicura. L’host, che in questo caso è il PC, può essere dotato sia di Windows che di Linux. Tra le caratteristiche di spicco di questo kit di sviluppo si ricordano:

- Dimensioni 10cm x 20cm.

- Processore ARM926EJ-S.

- Tre connettori Ethernet.

- 32MB di SDRAM on-board (espandibile fino a 64MB).

- 8MB di Flash.

- Connettore porta seriale (DB9).

- Porta JTAG.

- Doppia alimentazione on-board.

- Sistema operativo Linux.

- Bootstraps gestibile tramite DIP switch (la Figura 5 mostra la presenza di appositi interruttori per gestire i registri di bootstraps).

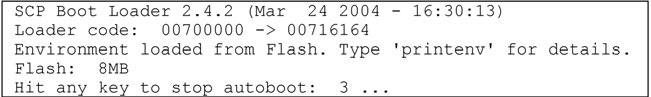

Tra i vari componenti presenti, è importante evidenziare U12 che è una ST Flash da 8MB in package TSOP e U13 che invece è una Flash Atmel da 256KB in package PLCC. Il primo supporto di memoria può contenere sia il codice ARMBoot che l’immagine Linux, mentre il secondo soltanto il codice ARMBoot. Inoltre, la ST Flash è il solo dispositivo che può essere programmato in-circuit, mentre per eventuali aggiornamenti della memoria Atmel è necessario disporre di un programmatore apposito. Per quanto riguarda i supporti di memoria volatili (RAM) la scheda è dotata di due banchi da 128Mbit (= 16MB) di SDRAM prodotti da Micron (modello 48LC8M16A2). Dopo che la scheda è stata alimentata e connessa tramite cavo seriale null-modem ad un PC, il codice ARMBoot inizierà l’esecuzione. Se viene premuto un tasto la scheda interromperà l’esecuzione del codice e il S.O. Linux non sarà caricato. La schermata che compare in questo caso è riportata in Figura 6.

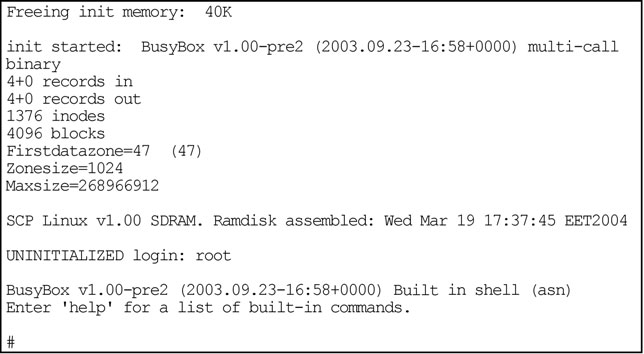

Se nessun tasto viene premuto, la scheda avvierà Linux. Dopo che è terminato il boot, è necessario digitare root seguito da Invio. Ora il S.O. Linux è stato effettivamente caricato. La Figura 7 mostra un estratto della schermata in questione. Se invece è stato eseguito l’ARMBoot sono disponibili un gruppo di comandi per il programmatore, in un ambiente DOS-like.

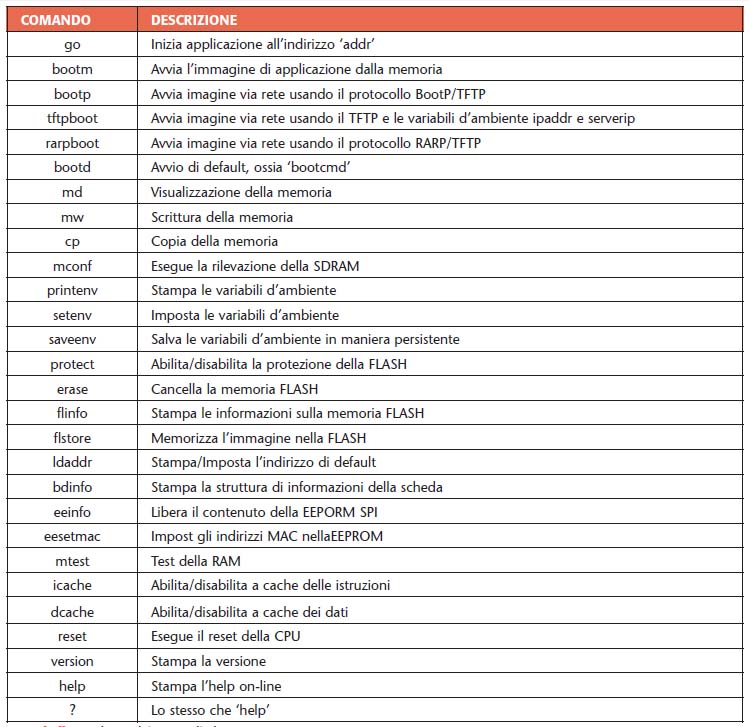

Per avere una lista completa dei comandi è possibile utilizzare il comando help oppure ?. Per avere ulteriori informazioni su un comando è possibile usare la sintassi help <comando>. L’elenco completo è riportato in Tabella 8.

Tipiche applicazioni in cui bisogna usare il prompt ARMBoot sono quelle dell’impostazione e della visualizzazione degli indirizzi MAC. Essi sono contenuti nella EEPROM. La scheda di sviluppo per MCS1000 presenta tali indirizzi già precaricati. Un esempio di ciò che potrebbe restituire il comando eeinfo è riportato in Figura 8.

In particolare, i MAC vengono memorizzati a partire dall’indirizzo 0x100 (default), ma questo non è un requisito vincolante. Per impostare gli indirizzi MAC, invece, deve essere usato il comando eesetmac. Ad esempio, per impostare l’indirizzo della porta Ethernet 1 al valore 0030138A568E si utilizzerà la seguente sintassi:

eesetmac 1 00:50:c2:19:c0:b8

Il pezzo forte di questo micro è stato proprio la sicurezza, forse poi non ha trovato spazio nel mercato però inizialmente ha avuto un buon interesse. Le board di sviluppo permettono di fare cose interessanti anche a livello industriale.