In questo articolo per la rubrica Firmware Reload, analiazziamo le caratteristiche principali della suite di sviluppo per FPGA Xilinx.

Introduzione

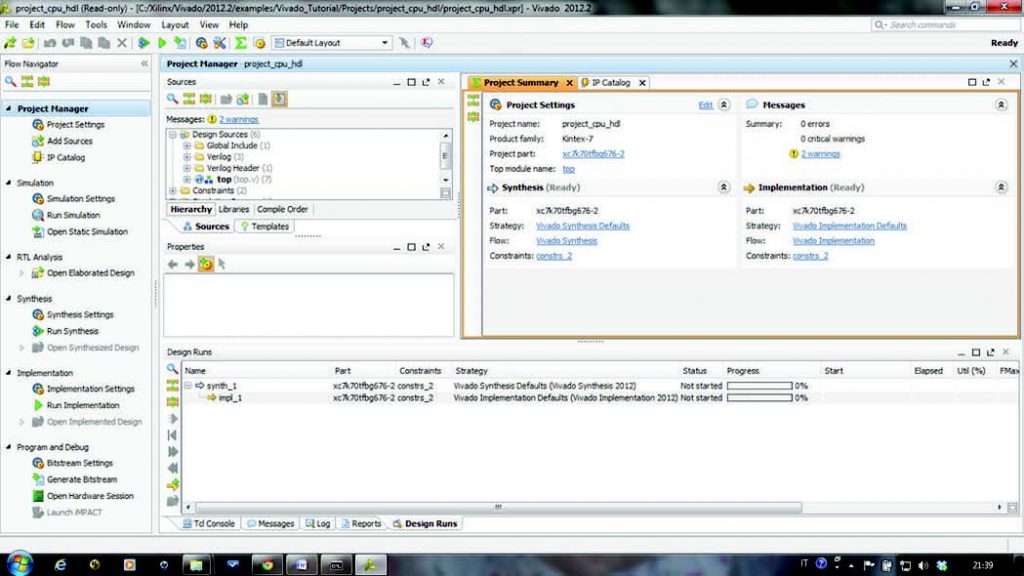

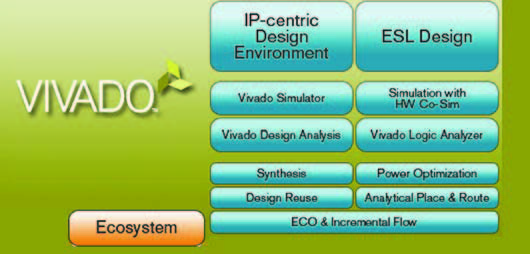

La crescente capacità logica dei dispositivi programmabili oggi disponibili sul mercato e la conseguente complessità dei sistemi in essi implementati richiede l’impiego di tool di progetto con funzionalità sempre più avanzate, così da poter ridurre i tempi di sviluppo ed integrazione. Vivado è la nuova suite di Xilinx per la progettazione con i più recenti dispositivi delle serie Virtex-7 e Zynq-7000. Affianca al momento l’ambiente tradizionale ISE ma è previsto diventi nel prossimo futuro la sola piattaforma di sviluppo per FPGA Xilinx. ISE resta la suite da utilizzare per tutti i dispositivi fino alle serie 6 ma supporta comunque anche le nuove famiglie 7 per quanti non vogliano migrare ancora verso i nuovi tool Vivado. Vivado supporta il tradizionale flusso di progetto con dispositivi FPGA (in modalità batch con supporto per programmazione Tcl o mediante interfaccia grafica, mostrata in Figura 1) integrando, come mostrato in Figura 2, soluzioni per design entry, simulazione, sintesi e place&route, programmazione e debug in circuit ma adotta un nuovo approccio IP-centrico e supporta funzionalità ESL (Electronic System Level Design) per una maggiore produttività.

Il risultato è una accelerazione dei tempi di sviluppo ed integrazione del proprio progetto fino anche un fattore 4, una riduzione dei tempi di simulazione di un fattore 100 per test-bench in linguaggio C e di un fattore 3 per simulazioni RTL (supportando anche co-simulazione hardware), una migliore utilizzazione delle LUT delle FPGA con una riduzione di logica occupata fino al 20% e fino al 35% della conseguente potenza dissipata, grazie ad un nuovo algoritmo di placer analitico. La configurazione base Vivado Design Edition include tutti i tool di progetto per sistemi logici ed embedded mentre la soluzione estesa Vivado System Edition supporta soluzioni HSL (High Level Synthesis) sotto Matlab, Simulink e per C/C++/SystemC oltre ad integrare anche il tradizionale ambiente Systems Generator for DSP disponibile già nella precedente suite ISE.

Figura 1. L’interfaccia grafica del nuovo ambiente Vivado di Xilinx

UN APPROCCIO IP-CENTRICO

Vivado supporta, come detto, tutti i tradizionali metodi di design entry per descrizioni RTL o netlist o le nuove metodologie HSL di più alto livello ma diversamente dalle soluzioni precedenti, adotta un approccio IP-centrico che semplifica creazione, integrazione e riutilizzo di IP core proprietari o di terze parti. Il riutilizzo di core IP e l’adozione di metodologie HSL rappresenta infatti oggi l’unica soluzione per contenere i tempi di sviluppo di sistemi complessi in FPGA di elevata capacità logica. Vivado IP Integrator, in particolare, è l’ambiente di sviluppo grafico che facilita la definizione di architetture gerarchiche e l’interconnessione di core con interfaccia AXI, il nuovo standard per sistemi on-chip di AMBA supportato anche dalla nuova famiglia Zynq di Xilinx di FPGA con processore ARM embedded. L’interfaccia grafica riduce i tempi di integrazione e le possibilità di errore.

IP Integrator supporta funzionalità di cross-probing per debug e script Tcl. IP Catalog è quindi la libreria di core IP disponibili per il proprio progetto ed include sia moduli proprietari che di terze parti. Core creati in IP Integrator possono essere salvati all’interno del repository di IP Catalog per il successivo riutilizzo, migliorando così l’efficienza di progetto. IP Packager consente quindi l’integrazione delle descrizioni RTL/HSL del core IP con eventuali metadata accessori, come file di constraint o di documentazione, testbench di verifica funzionale, esempi di riferimento e script per sintesi e place&route; supporta lo standard IP-XACT (la specifica creata originariamente dal consorzio Spirit e successivamente standardizzata sotto l’egida IEEE come IEEE Std 1685-2009 e che definisce un formato XML per la creazione di datasheet elettronici) e la modalità IEEE P1735 per la gestione di file di progetto criptati per la protezione della proprietà intellettuale.

Figura 2. Vivado Design Suite supporta l’intero flusso di progetto con FPGA

SUPPORTO PER TOOL HSL

Vivado High-Level Synthesis è il tool di sintesi di alto livello incluso nella suite Vivado, che eredita le funzionalità principali della precedente soluzione AutoESL. Consente l’astrazione della descrizione di algoritmi complessi in linguaggi C/C++/SystemC, ad un livello più alto rispetto a quello reso possibile dai tradizionali linguaggi HDL orientati alle descrizioni RTL. Vivado High Level Synthesis supporta i principali costrutti standard dei linguaggi C/C++/SystemC, la definizione di tipi di dati interi o frazionali a virgola fissa o mobile e con precisione definibile dall’utente, la capacità di inferire interfacce di comunicazione di tipo standard (fifo o AXI) o definite dall’utente. La fase di verifica è accelerata dal supporto di test-bench in linguaggio C/C++ riutilizzabili pure per la validazione della descrizione RTL estratta, grazie alla generazione automatica di opportuni wrapper SystemC. Vivado High Level Synthesis è perfettamente integrato con il repository IP Catalog di Vivado e il tool System Generator for DSP per la progettazione sotto Matlab/Simulink. Tale tool supporta la generazione automatica di codice da modelli Matlab/Simulink creati mediante integrazione di macro-blocchi disponibili all’interno dei diversi repository ed è ideale per i progettisti di applicazioni di digital signal processing abituati a lavorare con i tool di Mathworks.

VERIFICA E DEBUG

Vivado include un nuovo simulatore (la cui interfaccia grafica è mostrata in Figura 3) di tipo event driven per descrizioni HDL; supporta i linguaggi VHDL e Verilog come pure descrizioni miste. Al solito, il tool è interamente integrato all’interno della nuova suite semplificandone così le modalità di utilizzo. Il simulatore supporta compilazione multi-thread del codice, compilazione incrementale e ottimizzazione di codice compilato per una riduzione dei tempi di verifica funzionale di progetti complessi. Include librerie precompilate per le hard macro disponibili nei dispositivi Xilinx e dispone di viewer di forme d’onda analogiche ed editor di memoria. Interessante è, inoltre, il supporto integrato per co-simulazione hardware, che consente l’offload di parti di codice su hardware reale, sia per quanto riguarda il progetto della FPGA che il test bench stesso di simulazione, per accelerarne la fase di verifica; i tempi di debug risultano ridotti di un fattore fino oltre 100. La suite Vivado Logic Analyzer eredita invece le funzioni tradizionali della soluzione di debug in circuit Chipscope Pro, consentendo l’inserzione di core logici all’interno del proprio design (come descrizione HDL o netlist precompilate) per il probing di segnali e l’I/O virtuale. Vivado Serial I/O Analyzer è invece il tool di supporto per la verifica in circuit dei link di connessione seriale high-speed basati su transceiver integrati.

Figura 3. Vivado Design Suite integra simulatore event-driven mixed language e viewer di forme d’onda analogiche

DESIGN IMPLEMENTATION

Oltre che migliorare le metodologie di design entry, le nuove soluzioni incluse in Vivado Design Suite accelerano anche la fase di implementazione, riducendo i tempi di sintesi e place&route di un fattore fino a 4 e la richiesta di memoria di un fattore 2 rispetto a quanto riscontrabile con tool analoghi di altri vendor. Il motore di sintesi, di tipo timing driven, supporta descrizioni in linguaggi VHDL, Verilog e SystemVerilog ed è ora compatibile con il formato SDC (Synopsis Design Constraint), lo standard principale oggi utilizzato dai vendor di soluzione EDA per la definizione di constraint di sintesi, clocking, timing, power e test. Integra classiche funzioni di cross-probing tra la descrizione HDL e lo schema circuitale, rappresentato sia a livello RTL che in termini di primitive sintetizzate della tecnologia target. Dispone di Timing Analyzer che consente di analizzare i path critici dal punto di vista dei ritardi temporali, consentendo di evidenziare direttamente nel codice sorgente le relative descrizioni.

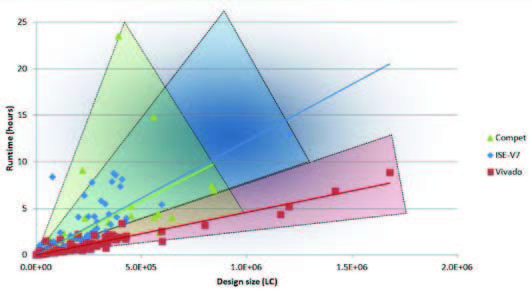

Ciò permette di determinare piuttosto facilmente le funzioni logiche principali che influiscono sulla massima frequenza di funzionamento del proprio circuito, favorendo l’adozione di un approccio incrementale al progetto fin dalle fasi iniziali di design. Decisamente migliorato è anche il motore di place&route che utilizza ora un approccio multi-variabile. Rappresenta, ovvero, lo spazio delle soluzioni di piazzamento del circuito sintetizzato in una funzione di costo a più variabili, dipendente da fattori come il timing del circuito, la lunghezza dei path di connessione e la metrica di congestione del dispositivo; quindi adotta un algoritmo analitico di ottimizzazione di questa per individuare la soluzione migliore rispetto a tali parametri. La Figura 4 mostra i vantaggi di un tale nuovo approccio rispetto alle più classiche soluzioni, come quella disponibile in ISE e in tool analoghi di altri vendor.

Figura 4. Vivado Design Suite implementa un motore di place&route analitico basato su funzione di costo multi-variabile

E' interessante come le prestazioni in termini di tempo di esecuzione sono lineari rispetto alla dimensione del circuito sinterizzato (fino anche per design di complessità logica oltre i 10 MGate) e quindi facilmente predicibili. L’ambiente di place&route supporta infine funzionalità avanzate di ECOs (Engineering Change Orders), consentendo di modificare alcune funzionalità del circuito dopo l'implementazione; è, ad esempio, possibile cambiare il piazzamento di alcune istanze o il path di net di connessione, come pure i parametri dei DCM o le funzioni logiche implementate da un LUT, il tutto senza necessità di ripetere le fasi di sintesi e place&route del flusso di progetto. Le modifiche possono ovviamente essere salvate in un file Tcl consentendo la creazione di script ripetibili in successivi tentativi di implementazione.