Esempi pratici di progettazione di alimentatori utilizzando il tool WEBENCH FPGA Power Architect di National Semiconductor.

La presenza negli odierni FPGA di un gran numero di carichi, tende a complicare il progetto del sistema di alimentazione. Oltre ai valori di correnti e tensioni richiesti, ogni carico può avere specifiche particolari in termini di tensione di ripple, filtraggio del rumore, separazione degli alimentatori e avviamento graduale (soft start). Molto spesso è necessario il ricorso ad alimentatori a commutazione c.c./c.c. ad elevata efficienza a causa degli elevati valore di corrente in gioco, mentre nel contempo è richiesto un controllo accurato del ripple e del rumore. L’architettura di alimentazione scelta può richiedere la presenza di uno o più valori di tensione intermedi tra l’alimentazione d’ingresso e i regolatori POL (Point of Load). La scelta delle tensioni con tali valori e dei regolatori POL può influenzare l’efficienza, le dimensioni e il costo del progetto dell’alimentazione dell’intero sistema. Oltre a ciò, i singoli alimentatori possono essere ottimizzati per garantire il conseguimento degli obbiettivi prefissati. In questo articolo verranno analizzati i vari aspetti legati al progetto di alimentatori e illustrati alcuni esempi di differenti approcci sviluppati mediante il tool WEBENCH® FPGA Power Architect di National Semiconductor.

LE RICHIESTE DEGLI FPGA

Per dare inizio al processo di design, è necessario determinare i requisiti di potenza degli FPGA. Questo può risultare un compito difficile a causa del gran numero di documentazione che è necessario analizzare.

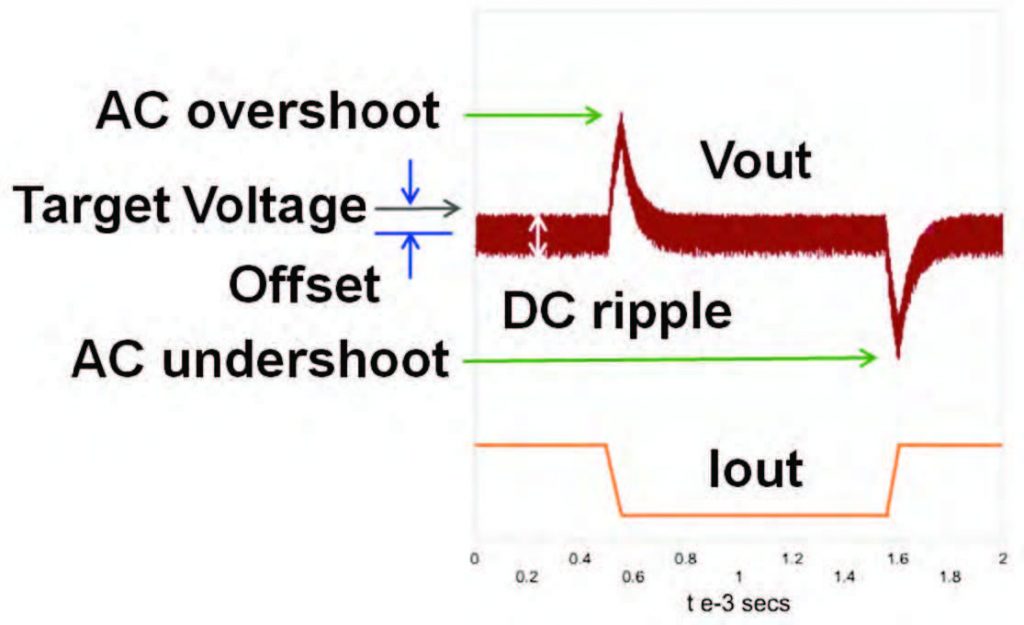

Al fine di determinare la corrente per ogni carico, parecchi costruttori di FPGA forniscono spreadsheet relativi alla stima della potenza. Essi calcolano i consumi di potenza e le correnti di carico in base alle risorse usate all’interno dell’FPGA. E’ anche possibile utilizzare simulatori più sofisticati, resi disponibili dai medesimi produttori. Dopo la stima delle correnti di carico è buona norma aggiungere un margine di sicurezza del 25%. Un altro requisito sono le specifiche di tensione relative al carico. Queste possono essere espresse semplicemente in termini di tensione massima e minima nel datasheet dell’FPGA. Ma dal punto di vista dell’alimentazione, è necessario prendere in considerazione numerosi fattori. Tra questi si possono annoverare gli offset imputabili alla rete di resistori di retroazione presente nell’alimentatore, le tolleranze dei resistori e la tolleranza del riferimento di retroazione del regolatore. Inoltre, è necessario prendere in considerazione il ripple del regolatore a commutazione che risulta composta da una componente nello stato stazionario e dalle sottoelongazione e sovraelongazione dei transitori. Senza dimenticare la possibile presenza di rumore di commutazione ad alta frequenza (a frequenze di 10 MHz o superiori). Nella figura 1 viene riportato l’andamento della forma d’onda relativa alla simulazione del transitorio di carico, ottenuto mediante il software WEBENCH FPGA Power Architect, di un tipico alimentatore a commutazione.

Figura 1: la simulazione del transitorio di carico ottenuta con WEBENCH FPGA relative a un tipico alimentatore a commutazione evidenzia i differenti elementi che contribuiscono a definire i valori di Vout.

Nel caso di carichi sensibili come i PLL, potrebbe essere richiesto un filtro separato per ridurre il ripple. Un’altra decisione riguarda l’opportunità di raggruppare carichi separati su un unico alimentatore – con conseguente diminuzione dei costi – oppure no, opzione questa che potrebbe essere richiesta in presenza di carichi sensibili al rumore. L’avviamento graduale può essere usato per consentire la sequenzializzazione (ovvero un’alimentazione entra in azione prima di un’altra), operazione che evita l’insorgere di fenomeni di blocco (latch-up), oltre a limitare le correnti di spunto e garantire un aumento monotonico della tensione. In definizione l’operazione di raccolta delle specifiche degli FPGA richiede un’esaustiva ricerca su un gran numero di documenti e un’attenzione particolare alle numerose note poste a margine. Tool di progettazione, come WEBENCH FPGA Power Architect, semplificano questo processo in quanto rendono disponibili tutte le informazioni necessarie in un unico luogo una volta effettuata la scelta dell’FPGA.

ARCHITETTURE DEI SISTEMI DI ALIMENTAZIONE

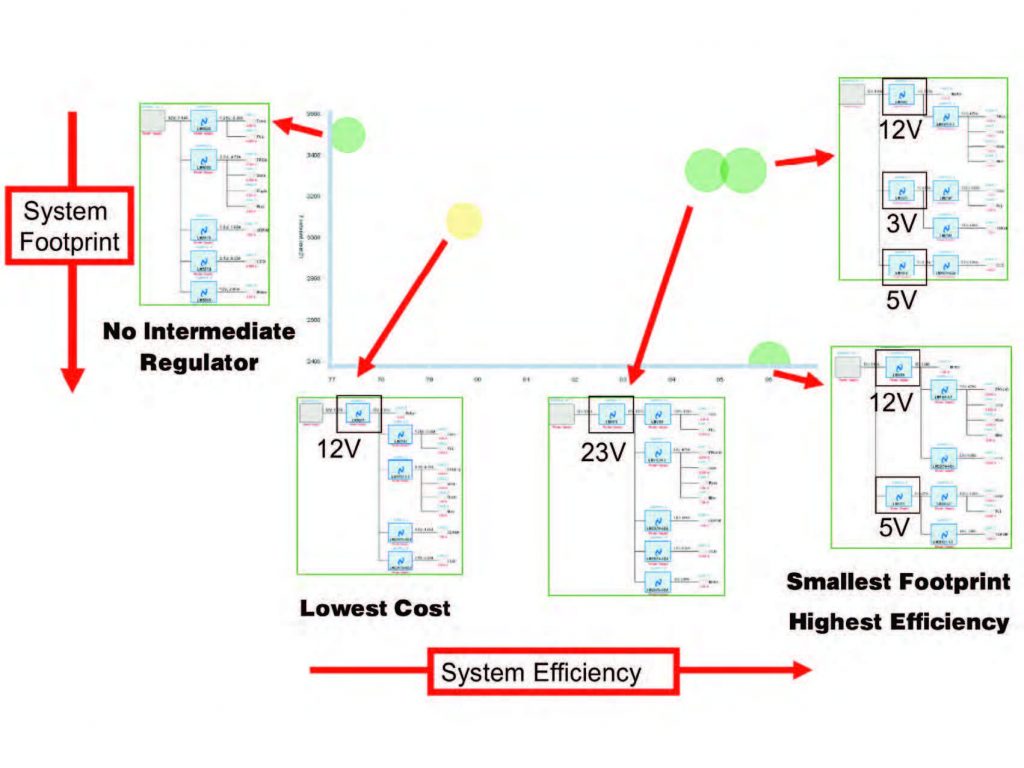

Una volta ottenuti i requisiti relative all’alimentatore, è possibile determinare l’architettura dell’albero (o del diagramma) di potenza (power tree). L’utilizzo di uno o più valori di tensione intermedi tra la sorgenti in continua e i regolatori POL può risultare vantaggioso. Uno dei motivi è dato dal fatto che esiste solo un regolatore che richiede componenti a tensione più alta che quindi risulterà più costoso e caratterizzato da maggiori ingombri. I regolatori step down asincroni che utilizzano MOSFET high side ad alte prestazioni, inoltre, tendono a operare in modo più efficiente per duty cycle più elevati. L’utilizzo di un regolatore intermedio aggiuntivo per ridurre la tensione di ingresso può dunque garantire una maggiore efficienza. Nella figura 2 vengono riportati esempi di alcune configurazioni con valori intermedi che hanno il medesimo ingresso e gli stessi carichi.

Figura 2: questo grafico, ottenuto con WEBENCH FPGA Power Architect, mostra varie architetture di alimentazione con le differenti alternative in termini di efficienza, dimensioni e costi. Sull’asse delle X è riportata l’efficienza, mentre su quello delle Ysono riportate le dimensioni, il diametro del cerchio, invece, fa riferimento al costo della lista dei componenti (BOM).

Come si può vedere dalla figura, l’opzione caratterizzata dagli ingombri maggiori e dalla minore efficienza, è quella che non prevede un valore intermedio, anche se ospita il minor numero di regolatori. Il progetto che prevede due valori intermedi di 12 e 5V, prossimi alle tensioni del punto di carico, sono invece ottimizzati in termini sia di efficienza sia di dimensioni.

DIFFERENTI ALTERNATIVE

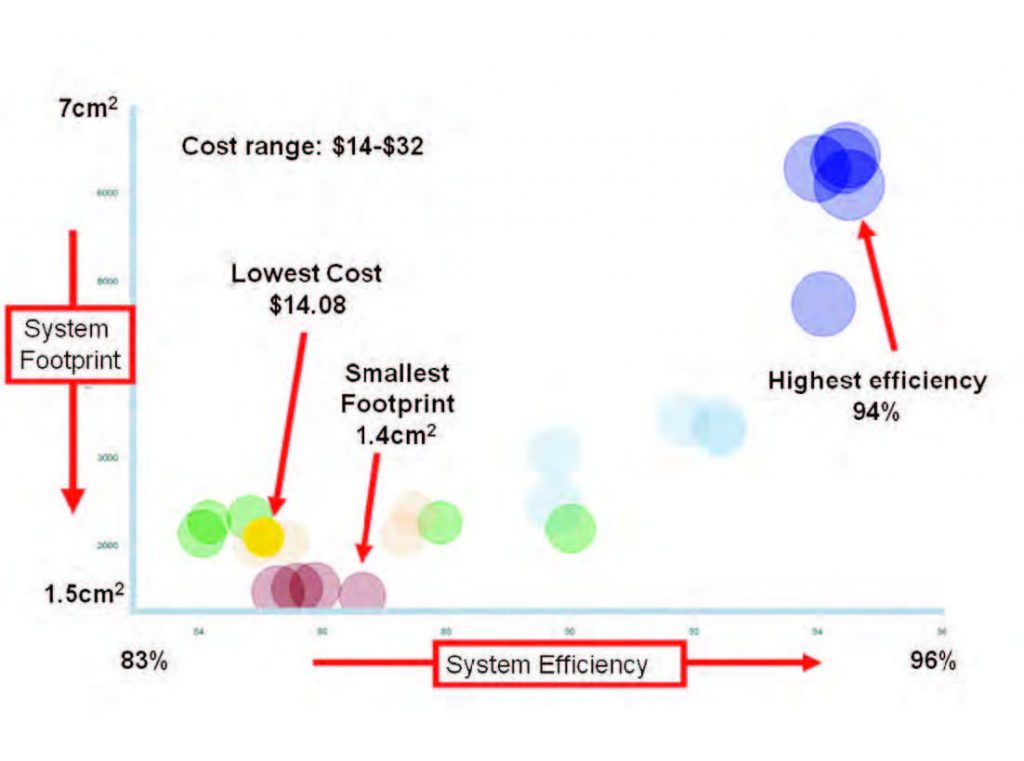

Una volta esaminata l’architettura di sistema, è possibile concentrare l’attenzione sulle modalità di ottimizzazione dei singoli alimentatori a commutazione al fine di conseguire gli obbiettivi di progetto: dimensioni ridotte, elevata efficienza e basso costo. Un elemento di fondamentale importanza è la frequenza di commutazione. Ad alte frequenze è possibile utilizzare un induttore di dimensioni inferiori grazie al minore tempo di on del commutatore il che comporta una riduzione delle dimensioni. Per contro, si ha un aumento delle perdite di commutazione, a scapito dell’efficienza. I costi tendono ad essere inferiori alle alte frequenze in quanto i componenti di dimensione inferiori risultano solitamente più economici. All’altro estremo, una bassa frequenza di commutazione contribuisce a ridurre le perdite di commutazione in c.a. con un conseguente aumento dell’efficienza: in questo caso è necessario un induttore più grande per mantenere nei limiti imposti la corrente di commutazione di picco, il che si traduce in un aumento delle dimensioni. Inoltre, un induttore più grande sarà verosimilmente più costoso. Per ottimizzare i singoli alimentatori e conseguire l’obiettivo prefissato, è necessario adattare l’intero sistema di potenza dell’FPGA. Nella figura 3 viene proposto un grafico, sempre ottenuto mediante WEBENCH FPGA Power Architect, di differenti soluzioni di alimentazione per FPGA che prevedono sia variazioni architetturali a livello di sistema sia ottimizzazioni singole.

Figura 3: le varie alternative possibili in termini di costo, efficienza e dimensioni relative a differenti sistemi di alimentazione per FPGA.

I livelli di efficienza dei sistemi variano tra l’84% e il 94%, gli ingombri della soluzione sono compresi tra 1,4 e 6.4 cm 2 mentre il costo della lista dei componenti è stimata tra 14.08 e 31.53 dollari. Visualizzazioni di questo tipo consentono ai progettisti del sistema di alimentazione di scegliere il miglior approccio a livello di sistema per conseguire gli obbiettivi prefissati. Da quanto esposto, appare chiaro che il progetto di un sistema di alimentazione per FPGA è un compito molto complesso e il ricorso a strumenti come WEBENCH FPGA Power Architect può contribuire a semplificare notevolmente il processo di sviluppo. L’impiego di carichi di FPGA pre-configurati può fare risparmiare tempo prezioso nella ricerca dei requisiti del sistema di alimentazione. Il ricorso ad analisi e simulazioni iniziali permette di ottimizzare il progetto di un sistema di alimentazione per FPGA e consentire al progettista di conseguire i propri obbiettivi in termini di efficienza, dimensioni, costi e timeto-market.