La TPU, acronimo di Time Processing Unit, è un controller programmabile sviluppato da Freescale (ora NXP) e dotato di sistema di memoria e codice propri. Questo consente di eseguire temporizzazioni e gestione dei pin di I/O in maniera efficiente, indipendentemente dalla CPU. La TPU è sostanzialmente un “microcontroller nel microcontroller”, poiché contenuta all’interno dei chip Freescale delle famiglie MPC500 e MC68332. Le sue funzioni principali spaziano dal controllo delle temporizzazioni, alla gestione degli I/O, alla comunicazione seriale, al controllo motori. Una nuova versione del modulo TPU è conosciuta con il nome di eTPU (Enhanced TPU)

Introduzione

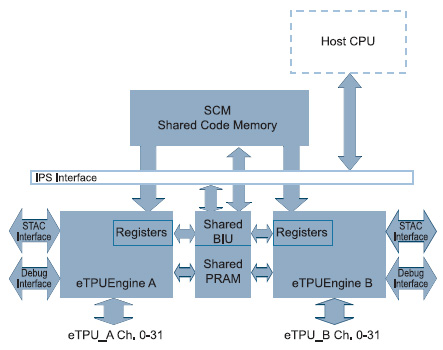

La nuova versione eTPU (Enhanced TPU) include un processore più potente, una gestione più efficiente del codice C, funzionalità e prestazione migliorate, un numero superiore di canali. Lo schema a blocchi di tale dispositivo è mostrata in Figura 1.

Figura 1: schema a blocchi della eTPU. Tale modulo costituisce una semplificazione notevole nello sviluppo dei propri progetti, poiché consente di sostituire vari circuiti e dispositivi esterni

La casa produttrice fornisce una serie di librerie che costituiscono una buona base per sviluppare progetti custom, utili per le proprie applicazioni. Nel seguito dell’articolo si analizzeranno le caratteristiche distintive e le modalità di funzionamento della eTPU.

CARATTERISTICHE TECNICHE

Le principali caratteristiche di una eTPU sono:

- 64 canali complessivamente.

- Risoluzione del timer fino a 24bit.

- Memoria programma fino a 64kB.

- Memoria dati fino a 4kB.

- Allocazione flessibile della memoria dati per le funzioni.

- Supporto della Angle Mode.

- Supporto DMA ed interrupt.

- Supporto della modalità debug.

L’elenco delle possibili funzioni utilizzabili è davvero impressionante. Esistono quattro categorie fondamentali:

- Temporizzazione generica.

- Interfacce di comunicazione.

- Controllo motori.

- Automotive.

LA ENHANCED TPU

La eTPU è costituita principalmente da un microsequencer (µSeq) e dall’hardware per la gestione dei canali (ci sono 16 canali per la TPU e 64 per la eTPU). Il µSeq prepara i canali a rispondere in tempi brevissimi ad eventi che si possono verificare in maniera asincrona. Quando un certo evento si verifica, l’hardware della TPU autonomamente esegue le azioni per cui è stata programmata. Questo sistema consente di ridurre al minimo la latenza rispetto ad un modulo gestito interamente dalla CPU. Un esempio che aiuta a rendersi conto dei vantaggi offerti da questo modulo è una routine di conversione frequency-to-digital, utile per fare delle misure di frequenza di un segnale. In tal caso il microsequencer imposta uno specifico canale della TPU ad operare come edge detector (PPA) e quindi rispondere ad una transizione del pin di ingresso. Quando questa variazione si verifica, il µSeq incrementa un contatore relativo a quello specifico canale e reimposta l’edge detector. Dopo un numero prestabilito di conteggi, il µSeq interrompe la CPU e quest’ultima utilizzerà il registro dei conteggi per effettuare il calcolo della frequenza Questo meccanismo consente di raggiunge una risoluzione di 200ns sulla misura della frequenza, utilizzando, ad esempio, un chip della famiglia 68332 ed un master clock di appena 20MHz. La Enhanced TPU è stata progettata per superare le limitazioni imposte dalla TPU. Essa non è semplicemente una estensione, ma un’architettura riprogettata. La eTPU è tipicamente configurata come un array di 64 canali, con 2 engine che condividono la memoria programma, quella dati e l’interfaccia debug. Quanto appena descritto è ben sintetizzato in Figura 2.

Figura 2: la eTPU presenta un’architettura rinnovata rispetto al modulo precedente. La condivisione della memoria programma, dati e dell’interfaccia debug incrementa sensibilmente le sue prestazioni

La eTPU presenta miglioramenti rispetto alla TPU in molte aree: l’hardware dei canali, la memoria del microengine e i tool. I blocchi indicati con il termine di engine sono responsabili della gestione delle transizioni sui pin di ingresso, nonché della generazione delle forme d’onda su quelli di uscita. Ogni engine ha il suo microprocessore, l’hardware dedicato per elaborare i segnali sui pin di I/O ed effettuare l’estrazione (fetch) delle microistruzioni dalla memoria programma condivisa, indicata in Figura 2 dal blocco SCM (Shared Code Memory). La shared Parameter RAM (SPRAM) conserva i parametri di configurazione ed i dati: entrambi gli engine accedono a questa area di memoria condivisa. Il blocco BIU (Bus Interface Unit), mostrato in Figura 2, consente alla CPU Host di accedere ai registri della eTPU ed ai relativi banchi di memoria, per la configurazione o la lettura dei registri.

L’hardware dei canali

La TPU è dotata di 16 canali identici tra loro, ciascuno dei quali è provvisto di un capture e compare register. Il primo (capture) permette di catturare il valore del timer quando sul pin di ingresso si verifica un certo evento: fronte di salita o di discesa. Il secondo (compare) comporta una variazione dello stato logico sul pin di uscita ed una richiesta di interrupt al microengine. L’architettura della eTPU prevede un potenziamento del sistema capture/compare. Ciascun canale della eTPU è dotato, infatti, di due registri capture e due compare. I registri ed i bus sono larghi 24bit e ciò estende notevolmente il range dinamico di tutte le funzioni. I canali della eTPU sono configurabili in 13 modi differenti per soddisfare tutte le possibili situazioni di impiego.

La memoria

Inizialmente, la TPU fu progetta per essere una sorta di timer sovradimensionato, ma il concetto di unità di elaborazione multiple non era ancora stato sperimentato; così gli sforzi maggiori furono quelli di mantenere la dimensione del modulo (e quindi della memoria) la più piccola possibile. La TPU montata sul MC68332 disponeva di appena 2kB di memoria programma. Lo spazio destinato ai parametri di configurazione era di 200byte distribuiti tra i 16 canali. Qualche anno dopo il progetto originale, fu introdotta la TPU2 che era equipaggiata con una memoria di 8kB, mentre per i parametri di configurazione erano disponibili 256byte. La eTPU dispone di uno spazio di 16k microistruzioni, ossia 64kB di memoria programma, condivisi tra i due microengine. Una certa funzione può essere eseguita su entrambi i moduli, in contemporanea, senza degradazione alcuna delle prestazioni. Inoltre, ciascun canale può indirizzare fino a 512byte (128 parametri locali) e 2kB di parametri globali. Come si vede la eTPU è stata potenziata molto rispetto al progetto iniziale, diventando così un vero e proprio microcontroller nel microcontroller.

Set di microistruzioni

Ciascuna microistruzione della eTPU può eseguire fino a 3 microoperazioni in parallelo. Esistono 4 differenti formati di microistruzioni:

- Operazioni con SPRAM;

- Operazioni con ALU/MDU;

- Operazioni di configurazione e controllo dei canali;

- Operazioni di controllo del flusso.

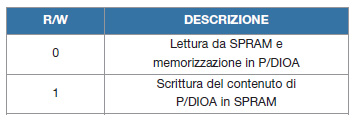

L’accesso alla SPRAM è fatto fornendo un indirizzo ed un registro per effettuare un trasferimento di dati. Soltanto i registri DIOB e P possono scambiare i dati con SPRAM; il registro DIOA ha dimensione 24bit, mentre P ha dimensione 32bit. A seconda dell’operazione di accesso alla RAM da utilizzare si può selezionare l’uno o l’altro registro, mediante il campo P/D (vedere Tabella 1).

Tabella 1: gli unici registri abilitati ad accedere all’area SPRAM sono DIOA (24bit) e P (32bit). La scelta di quale di questi utilizzare è fatta tramite il campo P/D

La direzione di trasferimento dei dati è determinata dal campo R/W in tutti i modi di indirizzamento: RW=0 seleziona la lettura da SPRAM, mentre RW=1 scrive in SPRAM (vedere Tabella 2).

Ci sono 3 modalità di indirizzamento in RAM:

- Assoluto.

- Relativo al canale selezionato.

- Indiretto.

Rientra pure nella categoria delle operazioni che effettuano un accesso a memoria quella di gestione dei semafori. In informatica, un semaforo è una struttura dati gestita da un sistema operativo multitasking per sincronizzare l’accesso a risorse condivise tra task (cioè processi o thread). È composta da una variabile intera e da una coda di task.

TOOL DI SVILUPPO

Quando la TPU fu progettata non ci si aspettava che venisse programmata, ma si pensava di utilizzare le funzioni assembler già caricate in memoria. Perciò i tool di sviluppo forniti a corredo erano limitati. Nonostante questo la TPU riscosse successo da parte dei programmatori che iniziarono a sviluppare tool di per facilitare questo processo. Per la eTPU vennero messi a disposizione, invece, una serie di strumenti di sviluppo che vanno dai compilatori con relativo ambiente di sviluppo ai debugger e simulatori. Byte Craft ha sviluppato un compilatore C ISO-compatibile che fornisce un’allocazione dinamica della memoria, una gestione ai riferimenti a variabile ed una semplificazione notevolmente dell’interfacciamento con la CPU. Ovviamente, l’uso del più complesso linguaggio assembly garantisce una maggiore flessibilità di programmazione. ASH WARE inizialmente ha sviluppato un simulatore per TPU. Visto il successo riscosso da tale strumento di sviluppo, la stessa Freescale si è avvalsa di ASH WARE per estendere la compatibilità del simulatore anche alla eTPU. Il progetto è avvenuto parallelamente a quello del chip per assicurare che il comportamento del simulatore fosse il più possibile rispondente alla realtà.

ESEMPIO DI UTILIZZO

Implementare una UART

La routine riportata nel Listato 1 mostra un esempio pratico di utilizzo della eTPU. Si tratta della procedura di inizializzazione per implementare sui primi due canali una interfaccia UART. In particolare, nell’esempio si utilizza l’engine A della eTPU e la funzione UART per effettuare la ricezione sul canale 1 e la trasmissione sul canale 0. La funzione è configurata per operare senza controllo di parità e con una lunghezza della parola di 8bit.

1. void init_etpu( ) {

2. volatile int temp;

3. // Inizializzazione dei registri di configurazione della eTPU:

4. ETPUMCR = 0x00070000; //SCMSIZE is 16K(7 2K blocks)

5. ETPUTBCR_A = (TCR1CLK_SOURCE_DIV2 | CHANNEL_FILTER_TWOSAMPLEMODE | TCR1_PRESCALER(8));

6. ETPUECR_A = (ENTRY_TABLE_BASE(0x1F) | FILTER_PRESCALER_CLOCK_DIV4);

7. //Selezione della funzione del canale da utilizzare tramite il registro (ETPUCxCR)

8. ETPUC0CR_A = (CHANNEL_INT_ENABLE|CHANNEL_FUNCTION(15)|CHANNEL_PARAM_BASE_ADDR(0x00));

9. ETPUC1CR_A = (CHANNEL_INT_ENABLE|CHANNEL_FUNCTION(15)|CHANNEL_PARAM_BASE_ADDR(0x02));

10.// Selezione della modalità di trasmissione

11.ETPUC0SCR_A = (FUNCTION_MODE(0)); // no parity for transmitter

12.ETPUC1SCR_A = (FUNCTION_MODE(0)); // no parity for receiver

13.//Scrittura in SPRAM per l’inizializzazione dei parametri dei canali configurati

14.MATCH_RATE_TX = MATCH_RATE_TRANS(0x412); // match rate per la trasmissione

15.DATA_UART_TX = DATA_WORD_TX(0x000000AA); // primo byte da trasmettere=AA

16.DATA_SIZE_TX = DATA_SIZE_TRANS(8); // 8bit per la parola trasmessa

17.MATCH_RATE_RX = MATCH_RATE_REC(0x412); // match rate per la ricezione

18.DATA_SIZE_RX = DATA_SIZE_REC(8); // 8bit per la parola ricevuta

19.// Inizializzazione dei registri di host service request (ETPUCxHSRR)

//per l’attivazione dei canali 0 e 1

20.ETPUC0HSRR_A = HOST_SERV_REQ(3);

21.ETPUC1HSRR_A = HOST_SERV_REQ(2);

22.// Impostazione priorità dei canali

23.ETPUC0CR_A =(ETPUC0CR_A | CHANNEL_PRIORITY_HIGH);

24.ETPUC1CR_A =(ETPUC1CR_A | CHANNEL_PRIORITY_HIGH);

25.// Per terminare l’inizializzazione

26.do {

27. temp = ETPUC0HSRR_A;

28.} while (temp != 0);

29.do {

30. temp = ETPUC1HSRR_A;

31.} while (temp != 0);

32.ETPUMCR = (ETPUMCR | GTBE);

33.}

| Listato 1 |